柏树半导体的PSoC刚出现时是革命性的。它使用了一个专有的8位核心,周围是可配置的数字和模拟块。这允许一个库存管理单元(SKU)根据应用程序和开发人员决定配置系统的方式来交付令人惊叹的外围设备组合。一种设计可能使用数字块作为定时器,而另一种可能使用它作为定制的串行接口。PSoC家族已经成长使用不同的核心和现在使用手臂Cortex-M内核。

PSoC 6是Cypress在2017嵌入式世界上发布的最新产品,它几乎和最初的PSoC一样具有革命性。有Cortex-M0+和Cortex-M4双核配置(图1).一个单一的Cortex-M4核心版本也将可用。双核系统允许一个核心作为安全处理器运行,完全控制另一个核心和外围设备的访问。

PSoC 6的故事更多的是关于双核解决方案。它仍然有可配置的数字和模拟模块,并有改进,但双核方法对安全性和低功耗运行有重大影响。150 MHz的Cortex-M4支持单精度浮点,100 MHz的Cortex-M0+可以在安全模式下运行。

有独立的电源管理和处理器间通信(IPC)硬件,加上共享SRAM支持。Cortex-M0+可以阻止Cortex-M4对内存块和外设接口的访问。该系统只需使用200µA。单片机有功功率为22 μA/MHz。深度睡眠模式可将功耗降低至4.5 μA。

Cortex-M0+管理可信执行环境(Trusted Execution Environments, TEE)。这些是多个基于硬件的安全区域。硬件安全支持还包括安全引导、安全密钥存储和使用CapSense接口进行随机化的真实硬件随机数生成器。每个芯片都有一个唯一的ID。

该系统将在未来的版本中支持HyperBus和SD卡,但它已经使用QSPI就地执行(XIP)支持,使用加密或非加密的芯片外存储。芯片内闪存最高可达1mb。RAM最高可达288k字节。每个核都有一个8kbyte的缓存。

模拟支持是重要的,芯片上的降压转换器到12位ADC和DAC。最初的芯片将有一对运放和两个比较器。PSoC 6将有一系列无线选项,从蓝牙低功耗5.0 (BLE)开始,并向Wi-Fi等其他技术转移。

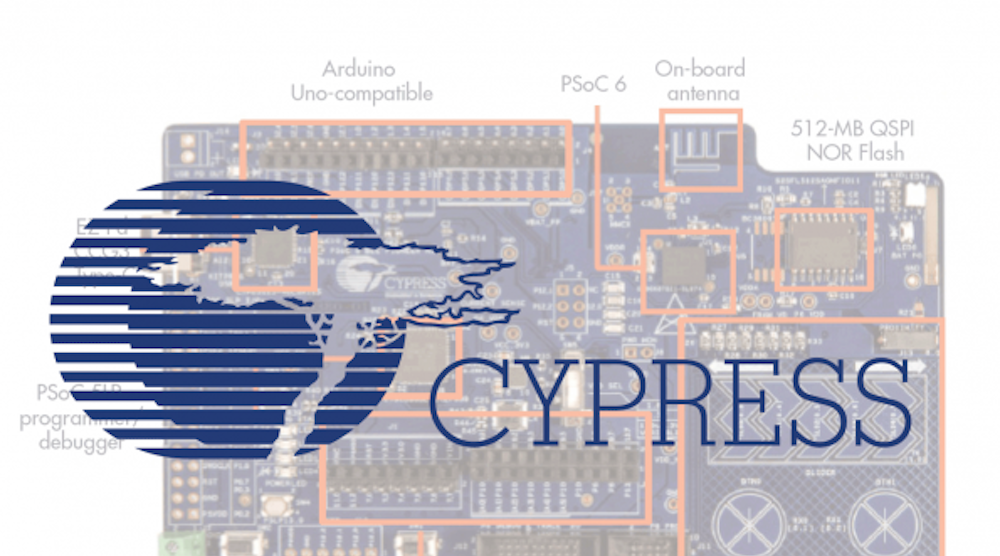

最初的PSoC 6开发工具包(图2)也令人印象深刻。当然,它有PSoC 6和PSoC 5来处理编程。它有一个USB Type-C接口,提供了一个高速接口,它还支持一个电源使用模型,外部电源可以通过Type-C连接器路由。Type-C支持实际上是独立于PSoC 6的,由柏树EZ-PD芯片.与之前的平台相比,该板的一个优势是,它可以测量PSoC 6的功率利用率

该板与Arduino Uno模块兼容。它有一个512mbit QSPI NOR闪存芯片和一个支持蓝牙的板载天线。Capsense触摸支持包括一个部分,可用于一系列按钮和滑块。

PSoC 6支持的一系列软件,包括PSoC Creator。还有一个公共的外围库,允许大多数PSoC特性被利用,而无需处理大多数定制芯片设计工具。