几十年来,软件开发人员受益于能够使用相同的软件代码,同时使用日益强大的硬件。由于硬件制造商经常通过提高晶体管密度和时钟速度来改善半导体的性能,软件开发享受了“免费便车”——他们能够在这些新设备上开发,而无需改变软件架构。

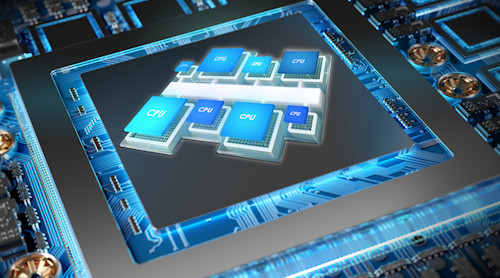

然而,由于增加的时钟速度的限制,处理能力遇到了瓶颈。因此,芯片制造商一直在转向戏剧性的新方法来实现进一步的性能提升。首先是超线程和同构架构,然后是异构的多核架构。为了从这些硬件更改中获益,现有的软件必须并行化和修改,以处理异构性。

现代的汽车微控制器(mcu)和片上系统,如英飞凌的AURIX 2G或英伟达的Drive Xavier,都指向了同质化,甚至异构的多核硬件架构的趋势。为了从硬件的进步中获益,汽车软件也需要改变。

在本文中,我将具体讨论如何标准化软件体系结构AUTOSAR的分层的软件架构,正在被当今功能强大的mcu所更新,以极大地提高性能。

为多核架构优化AUTOSAR

AUTOSAR软件体系结构的一个关键增强是将AUTOSAR通信堆栈分布在不同的核上,这是实现多核体系结构的性能优势的必要条件。

作为背景,在AUTOSAR 4.0.1中,首先介绍了对多核mcu的支持。在这次更新中,AUTOSAR提供了将应用软件组件(SWCs)分配到专用核心的方法,并通过运行时环境(RTE)促进了这些SWCs之间的跨核心通信。然而,AUTOSAR基本软件(BSW)仍然分配给单个核心。

在AUTOSAR 4.2.1中,AUTOSAR基本软件被划分为所谓的功能集群,这些功能集群可以使用BSW计划管理器(SchM)分配给不同的核进行核间通信。由于通信堆栈作为一个整体是这样一个功能集群,因此不支持在多个核上分布通信堆栈。而且,尽管AUTOSAR 4.4引入了分布最低层(微控制器抽象层)的BSW模块的可能性,但AUTOSAR通信堆栈的其余部分仍然必须放在单个核心上。

在AUTOSAR的发展过程中,分配给单个核的单片通信堆栈最终将成为性能瓶颈,这一点变得很明显。这是因为软件的顺序部分将继续对多核MCU实现的速度施加理论上的限制。因此,它导致了一种新的方法,将通信堆栈分布在不同的核上,这是获得多核性能优势的必要条件。

在处理通信栈软件分发时,为了有效地利用多核资源,考虑以下几点是很重要的:

- 尽量减少核间的通信和同步,因为它们通常涉及到核间中断,而核间中断反过来又会导致MCU操作模式的改变(从用户模式转换到监控模式)、流水线停顿和缓存丢失。

- 如果内核间的通话是必需的,而且无法避免,异步调用应该优于同步调用.后者会阻塞调用者,直到被调用者完成,从而降低了并行度,从而降低了潜在的加速。不幸的是,由于遗留问题,这并不总是可能实现的,因为AUTOSAR的通信堆栈大量使用了同步api,更改这些api将是一个主要的向后不兼容的重新设计。

- 此外,应该避免用锁实现的核间互斥如果可能,因为这将阻塞所有其他涉及的核心,而一个核心驻留在独占区域。由于自旋锁等典型的核间互斥原语涉及到繁忙的等待,这也会在阻塞的核上浪费CPU周期。

- 另一个重要的考虑因素是,大多数多核mcu所使用的非统一内存体系结构所需的代码和数据的适当位置。内存分为core-local内存(缓存、flash和RAM)致力于单一核心,可以快速访问和无冲突的核心,和全球内存(flash和RAM),不同核之间共享和访问该内存慢和冲突。在这种不统一的内存体系结构中,代码和数据的适当位置至关重要。频繁访问的代码和数据需要放置在尽可能靠近访问核心的地方。使用静态AUTOSAR内存映射机制,应该根据在实际负载场景下获得的访问统计信息来执行这种放置。

堆栈分配策略

考虑到这些因素,我们可以为AUTOSAR通信堆栈开发一般的分布策略。我们根据特定的网络类型(如CAN、LIN、FlexRay和以太网)将通信栈拆分为子栈,并允许每个子栈分配给一个专用的核心。因此,任何可能并发访问通信硬件外设(例如,CAN, LIN, FlexRay和以太网控制器)从不同的核心可以被排除。此外,不同的子栈可以完全独立和并行地执行,而不需要它们之间的交互。

为了进一步推动这种分离和独立性,我们将通信栈中的一般网络类型独立BSW模块(即IpduM和Com)拆分为不同的部分。每个部分都配备了一个专用的处理功能,该功能负责处理来自特定网络类型或针对特定网络类型的通信子集。然后将这些专用处理功能分配到相应网络类型的专用核心上。

通过这样做,我们有效地将特定网络类型的所有通信保持在单个核心的本地,并排除对任何其他网络类型通信的干扰。因此,我们避免了内核间的通信和同步,最大化了不同通信子栈的独立执行,并且能够将大部分AUTOSAR通信栈的同步API调用保持在各自内核的本地。

一种网络类型的通信路径(网关路由路径)和多种网络类型的通信路径(组播路由路径)都由具有多核能力的PDU路由器(PDU router)处理。PduR使用SchM的核心间通信功能来处理这些路由路径中所需的核心转换。PduR中的缓冲或排队有助于使用异步(而不是同步)内核间调用。这将导致调用者和被调用者的解耦,从而使不同网络类型的子栈的执行保持独立,即使对于这些通信路径也是如此。

这种AUTOSAR通信堆栈的核心分配导致了多核通信堆栈体系结构(见图).

这个多核通信堆栈架构是通过AUTOSAR堆栈的核心分配来实现的。

成功OEM实现

本文描述的方法已经成功地应用于一家德国汽车制造商的两个现实生活中的汽车系列项目中。第一个项目处理的是一辆高级车辆的中央网关电子控制单元(ECU),它需要在不同的网络之间路由大量数据,并显示出非常复杂的路由路径。在这个设置中,使用了意法半导体公司的Chorus 6M MCU,其中CAN、FlexRay和以太网子栈分别分配给专用的核心。

第二个项目涉及一个动力系统领域的主ECU,该主ECU显示出涉及多个ECU的时间关键事件链,并要求在多个CAN网络上严格确定定时。在这个设置中,使用了英飞凌AURIX 2G MCU,其中CAN和LIN子栈分配在一个核上,FlexRay和以太网子栈分配在另一个核上。

由于在这个项目中,跨越核心边界的通信路径的数量减少了,因此几乎没有可以测量的内核间通信和同步的开销(少于1%的额外CPU负载)。就内存映射而言,我们收集了现实负载场景下的访问统计数据,并针对频繁访问的代码和数据优化了内存映射。与未优化的内存映射相比,优化后的内存映射减少了15%的CPU负载。

总结

多核mcu的高效使用通常需要AUTOSAR基本软件的分布,特别是通信堆栈。我们提出按照不同的网络类型分割通信栈,防止通信硬件外设的并发访问,允许不同子栈的完全独立和并行执行,减少核间通信和同步的需要。

我们建议使用AUTOSAR的静态内存映射功能在内存中定位与各自核心具有很强亲和力的代码和数据,以正确使用快速的核心本地内存,并防止/减少访问较慢的全局内存时的冲突。该方法在德国一家大型OEM的两个系列项目中实施并部署表明,通过分配通信堆栈和合理分配应用软件组件,可以实现AURIX 2G MCU多核的高效利用。而且几乎没有核间通信和同步的开销。

托马斯·加拉博士是汽车网络的首席专家Elektrobit.