开放式连贯的加速器处理器接口(Opencapi)本周宣布闪存峰会,由OpenCAPI财团.它是一个新的高性能总线接口,专为服务器设计,现在具有开放内存接口(OMI)形式的内存语义。它与DRAM的标准存储器接口之间的巨大区别是以与PCI Express(PCIe)替换并行PCI总线的相同方式并行与串行的交换机。联盟由AMD,谷歌,IBM,Mellanox Technologies和Micron启动。

去年,IBM宣布新的Power9处理器将包含一个OpenCapi接口用于内存支持.其他处理器和GPU厂商是否会遵循这一路线将是很有趣的,但其优势与PCIe类似。

微芯片在满足存储需求方面处于最前沿。SMC 1000 8x25G PM8596芯片通过OMI接口作为内存的前端(图。1).传统并行接口和串行OMI之间的一个很大差异是接口是平台不可知的。OMI有一个抽象层;因此,控制器可以附加到不同类型的媒体。

1. SMC 1000 8X25G芯片支持DDR4 DRAM内存,同时提供标准OMI串行接口。

典型的DDR4-3200存储通道需要超过300个引脚,并且具有25 GB / s的带宽。单个OMI内存通道使用大约75个引脚,可以提供相同的25 GB / s吞吐量。4x OMI系统采用大量相同数量的PIN作为并行接口,但它具有100-GB / s的带宽或增加四倍。

Microchip的SMC 1000 8x25G控制器芯片支持X4和X8接口,使用OIF-28G-MR支持,使用25.6 GB / s串行链路。这包括动态低功耗模式。它位于17×17毫米的封装中,它可以接口NVDIMM-N持久存储器模块,以及多达四个级别的16 GB DDR4内存。板载开源固件处理DDR / OMI初始化并提供带内温度和错误监控支持以及对Chiplink GUI的支持。

SMC 1000 8X25G也提供安全性和数据保护服务。它可以支持硬件root-of tercor-secure启动和安全更新。还包括单符号校正/双符号检测ECC支持。该芯片可以处理带有错误的自动校正的存储器擦洗。

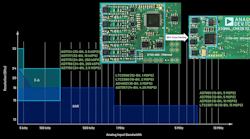

ddimm形状因子(图2)提供点对点8x25G OMI内存接口。这些DDIMMS支持DDR4 DRAM内存。DDIMM模块可从多个供应商提供,包括智能模块化,三星电子和微米,多种电容从16 GB高达256 GB。

2.这种DDIMM的外形设计支持一系列易失性和非易失性存储芯片。

使用OMI方法会带来优点,如更高的带宽和较低的引脚计数。通常,加载/存储操作由处理器内的存储器控制器排队。在这种情况下,存储器控制器集成在SMC 1000 8X25G内。Microchip的产品在设备延迟的领域创新,因此与LRDIMM延迟相比,较旧的并行DDR接口和此较新的OMI串行接口之间的延迟差异为4 ns。

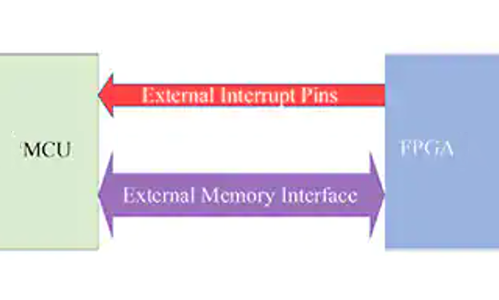

OpenCAPI联盟已经向联盟成员免费提供主机和目标OMI IP组件技术。这将被进一步采用,处理器、GPU和FPGA实现也将利用它的优势。同样,嵌入式应用程序对于这种类型的接口可能已经成熟了,特别是在单通道实现中,减少引脚数将是有利的。边缘计算对内存的要求更高,性能更好。