一个长期的支持者RISC- v(发音为RISC Five)指令集体系结构,Microsemi为其各种FPGA线路提供工具和RISC-V软核,包括最近发布的Mi-V(发音为My Five)生态系统。Mi-V进一步简化了RISC-V的开发,为软件开发人员提供了一个可以绕过FPGA设计过程的起点,同时为FPGA开发人员提供了一个更容易的基于RISC-V的设计起点(图1).

Mi-V生态系统包括Libero SoC IDE和软控制台IDE。前者是FPGA设计工具。后者是用于软件开发的基于eclipse的IDE。它附带了RISC-V工具集,所以使用它只是软件开发人员的问题。当然,生成定制的FPGA配置将需要使用Libero SoC。

1.Mi-V的RISC-V开发环境包括用于FPGA设计的Libero SoC IDE和用于软件开发的Soft Console IDE。

我已经试用了SiFive的hfie1,是一款核心RISC-V微控制器。使用它进行开发与大多数其他微控制器和微处理器平台相当。唯一不同的是RISC-V目标。

Mi-V的入门体验与HFive1相当,它允许软件开发人员快速启动和运行,而不需要处理FPGA的复杂性。这是通过提供预定义的配置来实现的。的Microsemi平台实际上有一个优势,即能够利用FPGA的闪存来处理代码和数据,从而实现一个自包含的平台。它还允许安全引导实现。此外,Mi-V还包括CoreBootStrap支持。

Mi-V支持多种Microsemi开发平台,例如基于igloo2的Creative Board(图2).该板包含三个常用接口的插座,包括PMOD、MikroBus和Arduino Shields。Creative Board有一个RISC-V平台和外围设备,因此软件开发人员几乎可以立即开始编程。

2.Microsemi它集成了一个IGLOO2 FPGA,可以轻松处理RISC-V软核。该板还具有PMOD、MikroBus和Arduino Shields的插座。

Mi-V生态系统实际上不仅仅是一个预先配置的RISC-V软核实现加上FPGA和软件开发工具。它包括一个版本控制的,用于匹配FPGA IP的驱动程序固件目录。这些驱动是MISRA和QNX中微子兼容的。

可能更重要的是RTOS支持,它提供了开源和第三方选项。开源选项包括FreeRTOS,华为LiteOS, Apache的MyNewt.第三方的选择是ExpressLogic的ThreadX和硅实验室MicriumµC/OSIII.

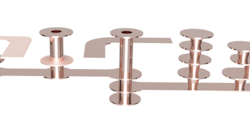

开发人员可以访问三个核心(图3).其中一个具有单精度浮点支持。目前还没有支持RISC-V用户模式选项。Mi_V_RV32IC_AHB是一个小型软核,使用大约4K LEs,包括调试支持。Mi_VRV32IMAC核心可以交付2.01EMMBC CoreMarks /兆赫这胜过了软竞争。

3.Mi-V环境最初支持三种RISC-V配置。

Mi-V代表了RISC-V的重大进步。RISC-V的开放特性使得它在军事和航空电子领域的应用非常有趣,在这些领域,开源RTL可以使认证变得更容易。

使用开源之类的工具可以生成新的RISC-V软核火箭芯片发电机.使用Mi-V核心的优点是它们已经配置和验证。