你将学习:

- 为什么传统的测试方法不能跟上今天的硅需求

- 最新的以软件为中心的方法如何降低成本和缩短上市时间

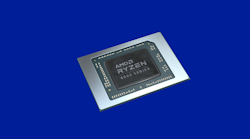

该行业可能刚刚开始使用400G光学器件,但芯片组制造商已经将目光投向了下一个产品:800G。将未来的超高密度数据中心、edge和5G网络解决方案推向市场的高风险竞赛已经开始。整个行业的利益相关者都在指望新一代应用专用集成电路(asic)和系统芯片(SOC)技术来帮助他们赢得竞争。

与所有的硅创新一样,通往未来芯片组的道路将涉及广泛的测试和验证。如果你是芯片组制造商、网络供应商和原创设计制造商之一,你将面临巨大的挑战。为了满足高压力的市场需求,您需要比以往更快地向市场推出新的解决方案,以更少的周期,理想情况下以更低的成本。你会想要避免芯片组制造中最昂贵的陷阱:在设计被放入硅之前而不是之后发现问题。

如果你正在努力想象你如何用当前的测试工具和方法完成这一切,你并不孤单。许多常见的测试方法几乎无法跟上今天的挑战,更明显。幸运的是,更好的选择已经开始出现。该行业终于开始基于连续的硅测试和硅后测试的更现代,以中心为中心的方法。这种过渡不可能在更美好的时刻来。

对新方法的迫切需求

随着云计算和边缘解决方案的市场计划,这些解决方案将为未来的超密集网络和超高性能应用提供动力,各公司都在觊觎最新和最好的硅。然而,设计和验证新的芯片组是一个众所周知的缓慢和昂贵的过程。

目前的硅开发周期包含了设计团队和制造商之间似乎无穷无尽的来回转换,通常是跨大洲的。这一过程持续数月,有时甚至超过一年,耗资数百万美元。这是在你没有发现发行后的主要问题的前提下。此时,您可以重新开始整个过程。直到现在,您已经浪费了数千个小时,扰乱了您的客户,并且(根据国家标准与技术协会的说法)将修复问题的成本提高了30倍。

为什么这个过程如此令人发疯?一个重要的原因是芯片组提供商继续依靠日期,低效的测试方法。许多仍然使用大型硬件的电子设计仿真(EDA)系统来模拟硅。这些系统确实提供了一种方法来验证IC和印刷电路板设计,但它们需要开发人员执行大量的物理测试,包括为每个端口和接口设置不同的测试。该过程可以如此艰苦,一些芯片组制造商完全支持大量的早期验证,这完全赞成硅后验证 - 尽管在高度采用的产品中发现了主要错误的巨大风险和成本。

更智能的前进道路

显然,许多芯片制造商一直在使用的测试工作流程应该进行彻底改革。该行业需要标准化一种更现代的方法,以更好地适应今天虚拟化的、以软件为中心的、云连接的技术环境。它可以让芯片制造商在生产过程的早期发现缺陷,并在它们最终生产出硅之前加以纠正。

好消息是,这种转变已经开始了。最新的硅仿真技术(目前处于第1层,未来将超越第1层)是降低设计过程成本和低效率的关键。通过减少对人工物理测试的依赖,支持仿真和自动化,芯片制造商可以极大地简化和增强前硅验证和后硅验证。在这个过程中,他们可以缩短几个月的上市时间。

现代EDA系统和仿真器抛弃了以硬件为中心的平台,转而支持更灵活的虚拟化软件。前硅测试工作流程也朝着同样的方向发展,基于硬件的流量生成器具有更灵活、更容易部署的软件解决方案。因此,芯片制造商现在可以快速测试数千个端口。而且他们可以轻松地、持续地重新配置测试,以在更短的时间内模拟更广泛的交通情况和协议。

现在可以在几分钟内执行用于设置50小时或更长时间的复杂网络环境的测试。而且,由于现代基于软件的测试床更加自动化和可重复,因此工程师使用它们不再需要在测试设计中具有广泛的专业专业知识。不再需要掌握不同的脚本或写数百万行代码。这意味着芯片制造商可以在同一时间帧中进行更多的测试用例,同时急剧缩小回归周期。

明天是最具创新性的云,边缘和物联网应用程序将需要硅,以便在最苛刻的高密度方案中提供卓越的性能。这意味着提供新芯片组的压力更快,更可靠地将继续增长。幸运的是,测试方法终于远离了十年前的工作,并提供了今天需要什么芯片制造商和客户。

通过引入更多的虚拟化、自动化和连续的硅前和硅后测试,芯片制造商可以:

- 将新的ASIC和SOC解决方案迅速推向市场

- 降低开发周期和成本

- 通过在设计阶段期间识别和解决缺陷来实现更高质量的标准,而不是在它们被烘焙到硅后面

- 在硅预验证和硅后验证中启用更一致的可重复使用的测试

也许最重要的是,通过简化和现代化的测试,芯片制造商可以进行更详尽的大规模测试。这意味着他们可以继续开发更专业、更复杂的芯片组——更快、更有效、更高质量。与此同时,该行业将获得更强大的工具,为客户带来改变世界的技术创新。