三星电子的半导体代工事业部总经理崔世英(音)表示:“到2025年下半年,将开始生产基于未来2nm节点的芯片。三星代工.

三星2021年铸造论坛的公告,信号标志着半导体巨头计划与台积电和英特尔留在比赛中,尽管近年来芯片制造业务有多艰难,但仍然发展世界上最先进的过程技术。

三星与其最新技术节点面临挑战。铸造厂计划在2021年的下半部分的基于其3nm节点开始滚动筹码。但是,它已经被迫延迟进程 - 首先使用大门(Gaa)晶体管 - 到2022年初。

2-NM节点也将基于门 - 全部 - 什么行业内部内部人员有时呼叫“Nanosheet”-Transistors,这是一种完全新的架构,这些架构承诺性能和功率效率的主要增益。

在过去的十年中,三星及其竞争对手已经用一种称为FinFET的晶体管滚出芯片。这些晶体管通过将硅形凸缘置于硅的鳍状凸缘而形成,以用作通过微小电子开关行进的电流的通道。称为“栅极”的结构控制从“源”到晶体管中的“漏极”电极的电流输送。将电压施加到栅极开启或关闭。门覆盖在硅片上,在三个侧面围绕它并限制电力泄漏。

在竞争中推出更小,更快,更少的令人掌的处理器,例如英特尔,三星和台积电等半导体巨头每年收缩硅片,使得可以在芯片中包装更多的晶体管。但每次他们缩放晶体管时,新的挑战都会发挥作用,使计算更加困难。

因为栅极仅在三个侧面围绕矩形翅片,所以当晶体管关闭时,少量电流可以从底侧逸出。拒绝关闭完全浪费的晶体管并将其散发为可以加注芯片整体性能的热量。

铸造厂正在升级栅极全能技术,以减少从晶体管中泄漏的电流,并增加它可以安全处理的电流。与将栅极覆盖在晶体管的沟道区域并覆盖它的三面不同的是,翅片被翻转到一侧,这样金属栅极就可以围绕在沟道的各个侧面,从而限制了功率泄漏,并使其切换得更快。

晶体管的其他优点之一是芯片制造商可以调节内部带状通道的宽度。这让它们微调用于电源效率,性能或模具区域的晶体管。

三星表示,将在2022年上半年开始生产其客户的首个3nm芯片设计,而其第二代3nm节点预计将在2023年。其第一代独特的栅全能晶体管技术,被称为多桥通道FET或mbcet,与其5纳米FinFET节点相比,可减少35%的面积,提高30%的性能或降低50%的功率。

去年,三星成为首家宣布转向全门型晶体管的代工企业。今年7月,这家代工企业推出了首个3纳米测试芯片,标志着该公司终于接近量产。

英特尔计划从2024年开始推出其被称为RibbonFET的栅全能晶体管和20A工艺节点。今年7月,该公司表示,高通(Qualcomm)已成为其第一个20A硅代工客户。

它还在其第二代带状福特技术的早期工作开始于2025年的叫做18A的18A-of。

对新晶体管设计的过渡是半导体工业的巨大事业。

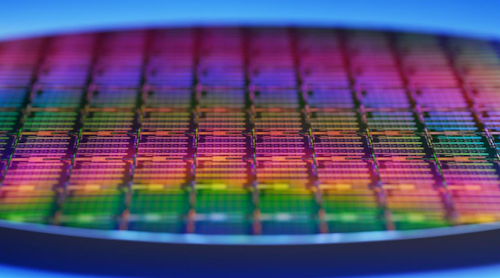

芯片铸造厂需要提高成品率——在晶圆厂加工的每片硅片中能够切割出的未损坏芯片的百分比——以达到技术节点盈利的程度。Cadence、Synopsys和其他软件供应商需要推出电子设计自动化(EDA)工具,以解决楼层规划、路由和布局的新规则,以及在高级节点上增加的变异性。

无晶圆厂的半导体公司也需要CPU核心和其他可以用GAA fet制造的ip。

三星在全球拥有世界上最大的代工业务之一,包括在韩国先进的S1、S3和S4晶圆厂,以及在德克萨斯州奥斯汀的S2工厂。英伟达利用三星为其数据中心市场生产旗舰产品A100 GPU。三星电子还与高通公司(Qualcomm)合作,生产用于5G智能手机的5纳米Snapdragon芯片。IBM是另一个关键客户。

提高其3纳米和2纳米节点的成本、面积、性能和功率将是使其客户不转向竞争对手并签订新合同的关键。

虽然该公司并未透露3nm工艺改进的具体细节,但基于2nm工艺的芯片可能会比上一代节点拥有健康的功率、性能和晶体管密度增益。三星表示,将利用在3纳米节点学到的知识来实现2纳米节点的目标。Choi说:“最终,我们预计该行业向2纳米过渡的过程会很顺利,这要归功于之前在3纳米技术方面的经验。”

三星的代工业的高管表示,它的过程“成熟度”增加了它的3-NM节点,其逻辑芯片收益率与其4-NM节点相同的级别,这是批量生产。

如果新节点在2025年的下半部分进入大规模生产,智能手机或来自三星筹码的其他设备可能不会在2026年第一季度之前达到市场。