Cadence推出了一套新的软件工具,称为Integrity 3D- ic平台。该公司表示,该平台可以帮助工程师开发基于3D封装技术的更快、更少耗电的芯片。

Cadence是世界上最大的电子设计自动化(EDA)软件供应商之一。它的软件工具自动化了大量的计算,这些计算需要在芯片中构建、配置和连接数十亿个晶体管,这样工程师就可以节省时间,并将精力集中在更重要的设计方面。它与英伟达(Nvidia)、AMD、高通(Qualcomm)和其他半导体领域的主要公司合作。

但现在,随着越来越多的客户从制造单片芯片转向在3D封装中堆砌更小的硅片片,该公司正试图在芯片设计过程的更多方面实现自动化。

这家总部位于加州圣何塞的公司表示,Integrity 3D- ic软件使其客户能够在3D芯片的平面图上自动放置模具。Cadence表示,客户还可以使用内部的热、功率、信号完整性、计时和其他分析工具,在设计早期识别出需要改进的地方,并验证芯片是否能在整个系统中工作。Cadence表示,Integrity 3D- ic帮助工程师们减轻了设计3D芯片时的头痛问题。

“这是3D IC设计所需的一切,”Cadence数字和签字组产品管理总监Vinay Patwardhan表示。

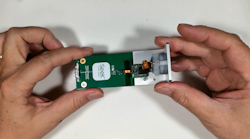

Cadence表示,客户多年来一直在使用Integrity 3D-IC旗下的许多软件工具。图1).但Integrity 3D-IC之所以脱颖而出,是因为它让客户能够从一个座舱中访问所有这些工具。这使得工程师可以共同设计芯片和封装它们的封装。

多年来,英特尔(Intel)、台积电(TSMC)和三星(Samsung)等半导体巨头一直在努力制造越来越小的晶体管,以便在单个芯片中装载更多的计算能力。但随着该行业在摩尔定律上越来越落后,他们也试图通过三维堆叠芯片,创造出逻辑和内存封装的微型摩天大楼,从而从硅中获得更高的性能和功率效率。

许多所谓的2.5D和3D封装技术也可作为代工服务,包括台积电的CoWoS和3D SoIC封装,以及英特尔的EMIB和3D foos技术。这为更多公司开发三维芯片打开了大门,而不是试图把所有东西都放在一个骰子上。

这种系统包内(SiP)策略打开了混合和匹配不同模具的大门,通常基于不同的节点,由不同的铸造厂生产。这与智能手机使用的系统芯片(SoC)模式形成了鲜明对比,在这种模式下,设备的大多数组件都可以装入一个芯片中。因此,2.5D和3D封装在晶体管密度、功率效率和成本方面都得到了回报。

通过将瓦片在三维空间中堆叠,工程师可以拉近包装中模具之间的距离。通过单个芯片内部的铜线远距离发射信号需要消耗更多的能量,降低带宽,并导致更多的散热。但芯片在3D封装中通过更短的死对死互连(称为微凸点),从而提高了功率效率和延迟。

但是,虽然堆叠更小的模具(或将它们放在硅插片上或通过硅桥连接它们)可以提高速度和功率效率,但这也给芯片设计带来了挑战。

在芯片的物理设计中,最重要的阶段是平面图的规划。这个过程需要在一个非常有限的区域内仔细配置数百甚至数千个内存和逻辑模块。选择每个部件的位置可以影响芯片的功率效率、处理速度和面积。一般来说,工程师会尽量将芯片中的布线量控制在最低限度,以控制电力使用。

地板规划是一个复杂的设计问题,往往需要花几个月的时间来微调芯片的蓝图。但是,在一个3D包中找出理想的芯片排列方式又给这个问题增加了一个维度。

为了加快3D设计过程,Cadence引入了完整的3D规划系统Integrity system Planner,玩家可以使用该系统拖放之前设计的砖块,并将其放入3D包中。它也可以画出模对模互连以及硅通孔缝合在一起的模具。Cadence表示,Integrity 3D-IC还可以进行物理验证,以检查模对模通信。

Patwardhan说:“你可以将模具安装到包上,你可以将高带宽内存(HBM)放在里面,然后你可以移动它们,从系统级别查看布局并进行优化。”

另一个关键特性叫做原生3D分区。该技术将一个完整系统的平面图放在芯片上,并自动将其切成更小的板,然后再重新组装,而不是将预先设计好的模具组装在一起。Cadence表示,3D分区工具是基于其武器库中的另一项名为混合布局的技术,该技术可以自动放置内存和其他宏,同时实现逻辑块的放置。这使得该工具具有更大的灵活性来改进芯片的二维平面图。

他说:“我们可以将内存和其他宏分离出来,从一个芯片中创建两个或更多的死芯片。”“通过将内存置于逻辑之上,就有办法节省电力和提高频率。”

如今,基于台积电(TSMC)的CoWoS、英特尔(Intel)的EMIB或其他2.5D和3D先进封装技术的芯片更像微型电路板,而不是手机和许多其他设备的核心芯片。不幸的是,这也使它们容易受到电源完整性、时序、热和其他系统级别的问题的影响,而芯片工程师很少负责这些问题。

Patwardhan表示:“这与2D设计完全不同。“对于大多数芯片设计师来说,3D系统还是个新事物。”

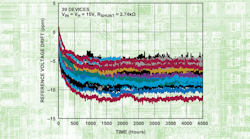

Cadence表示,Integrity 3D- ic还集成了Voltus、Clarity 3D瞬态求解器和Celsius热求解器,以运行信号和功率完整性(SI/PI)和电磁干扰(EMI)验证。Cadence还将引入Sigrity技术,以精确定位芯片和封装芯片的部分,这些部分可能会比其他部分更容易受热,从而导致热点,从而拖累性能。

该公司还将其Pegasus技术添加到该平台上,用于封装的模对模互连的物理验证。Cadence的Tempus软件可以运行静态时间分析和结束。

Cadence表示,他们设计了一个中央数据库,作为所有属于Integrity 3D-IC平台的不同软件工具的总机,这些软件工具都使用不同的数据格式。这样,客户就可以使用Voltus、Tempus、Pegasus和其他软件工具来了解不同3D设计的优缺点。然后,他们可以使用来自Integrity 3D-IC的反馈来重新排列封装中的模具,以提高功耗、性能和单个模具(如处理器模具)或整个系统的面积。

Cadence说,Integrity 3D- ic让工程师在将最终蓝图送到铸造厂之前,有更多的自由来试验3D芯片的平面图。通过将所有这些工具与Allegro封装和Virtuoso模拟技术整合在一起,Integrity 3D-IC可以让他们更紧密地合作设计模具和封装。这可以避免客户过度设计个人模具,以至于无法将其装入一个包装中。

Integrity 3D-IC的目标客户是在云数据中心使用的服务器处理器、网络芯片、交换机和加速器方面挑战极限的客户。Patwardhan表示,这些公司在3D芯片设计方面比其他公司更加积极。

Cadence的Integrity 3D- ic平台的早期用户包括半导体研究巨头Imec和Light Intelligence,后者是一家初创公司,开发了一种异构的3D硅光子处理器来运行人工智能。