Intel said it won a contract to supply leading-edge chip foundry services to the U.S. Department of Defense.

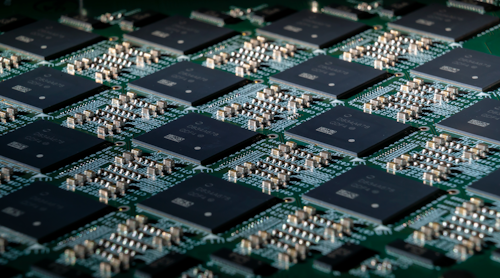

The contract was awarded last week as phase one of the DoD's Rapid Assured Microelectronics Prototypes Commercial program, or RAMP-C for short. Under the RAMP-C program, the agency is trying to guarantee it can use foundries located within the U.S. to get chips for aerospace and defense made on a state-of-the-art manufacturing node. It is partnering with Intel and other vendors to build the necessary foundry ecosystem.

英特尔首席执行官Pat Gelsinger说:“过去一年中最深刻的教训之一是半导体的战略重要性以及对美国拥有强大国内半导体行业的价值。”“英特尔是美国唯一的美国公司,既在领先优势上设计和制造逻辑半导体。”

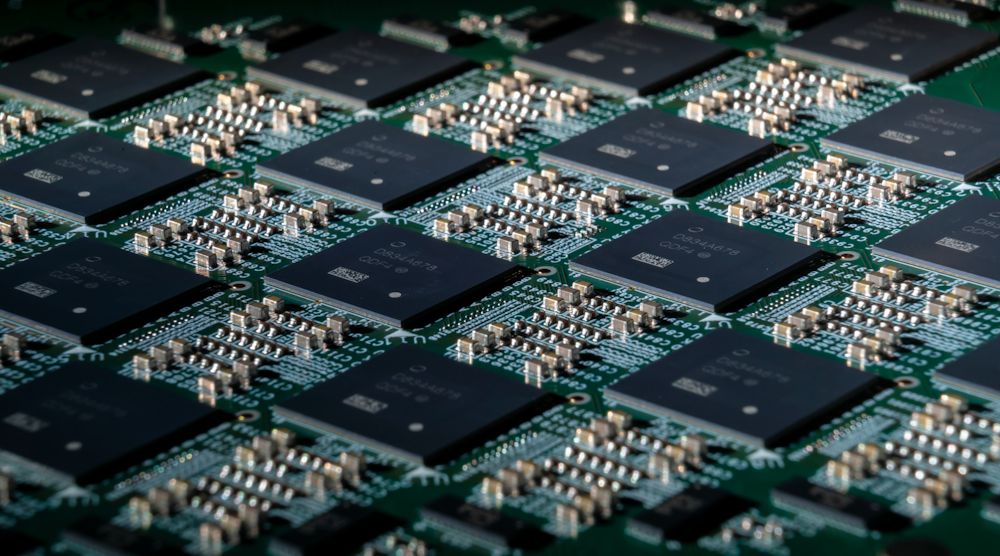

The U.S. accounts for only about 12% of global chip manufacturing capacity, as other nations have offered rich subsidies to encourage companies to build fabs. Furthermore, Intel has surrendered its ability to create the world's most advanced logic chips to rival TSMC, while Globalfoundries, the leading made-to-order chip foundry in the U.S., has halted the development of its most advanced nodes in favor of specialty processes.

Intel said the decline of semiconductor fabs in the U.S. is leaving the Department of Defense with limited onshore access to foundry technologies that can meet the nation's long-term needs for semiconductors.

The RAMP-C program will be led by Intel’s new foundry division, which it recently formed as part of a plan to regain its semiconductor crown by 2025. Intel said early in the year that it would build out a new business to make chips not only for its needs but also for other vendors (and even rivals) based on their blueprints. Intel Foundry Services is headed by Randhir Thakur, who previously ran Intel’s sprawling supply-chain operations.

英特尔表示,它正在与该计划的其他几家公司合作,包括世界上最大的电子设计自动化(EDA)软件制造商Cadence和Synopsys。IBM也正在参加该项目。尽管它多年来没有生产芯片,但IBM投资于有助于塑造半导体行业的研究。5月,它宣布它使用“纳米片”晶体管设计了世界上第一个2-nm测试芯片。

The deal with the Department of Defense looks far into the future. Intel said it would work with its partners to establish an ecosystem to design and test chips based on the Intel "10A" manufacturing node–the most advanced process on its roadmap–due for production in 2025.

Intel said the 10A node takes advantage of innovations it plans to roll out in the 20A node in 2024. One area of improvement is in the structure of the transistors themselves, Intel's first overhaul in more than a decade.

For years, Intel, TSMC, and other semiconductor giants have rolled out chips with transistors called FinFETs formed by placing fin-shaped protrusions between the source and drain sides of the channel. Transistors act as tiny electronic switches. The region that determines whether the switch is turned off or on—the gate—is draped over the fin, surrounding it on three sides and reducing the amount of power leaking from the device. These 3D transistors waste less power and, thus, operate faster and more efficiently than planar transistors.

Intel plans to move to a so-called gate-all-around transistor design called the RibbonFET starting in 2024. Instead of the fin partly covering the transistor, the fin is flipped on its side, so the gate surrounds a ribbon-shaped channel on all four sides, preventing even more power from leaking out. Intel said the RibbonFETs allow it to increase switching speeds at the same drive current as multiple fins in a smaller overall footprint.

英特尔的另一个功能是将其“背面发电系统”引入折叠。今天,最先进的逻辑芯片包含数十亿个晶体管。每一个都被互连的地板覆盖,这些互连的地板向晶体管供电,并向其他信号发送信号芯片上的晶体管,类似于微型塔中的楼梯间。互连是通过硅中的雕刻运河形成的,并用铜填充。

The problem is that the wires used for routing signals and relaying power to the transistors are tangled together, adding resistance that saps power efficiency. With PowerVia technology, Intel can instead bury the power rails behind the transistor instead of the front of the wafer. As a result, power can be delivered directly to the transistor above rather than traveling the long way through floors and floors of intertwined wires.

By placing the power rails on the underbelly of the transistor, PowerVia reduces resistance in the power delivery system. That results in less voltage dropoff from the power source to the transistors, allowing the chips to run cooler and more efficiently.

Powervia还允许专门用于信号路由的晶片前侧的电线,从而改善频率。

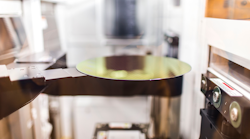

英特尔还计划利用10A节点中一种称为High Na Euv的新制造技术。作为其新工艺路线图的一部分,英特尔正在扩展EUV - 肖特用于极限脉络膜光刻 - 工具的使用,它们使用超短波长的光长度来烧焦硅的较小晶体管。这些系统以减少可能破坏最终芯片的不完美风险的方式工作,从而提高了收率。

But it is also trying to get ahead of rivals using a more advanced technology called high numerical-aperture (High-NA) EUV, which uses more concentrated beams of light to sear smaller transistor patterns on wafers.

英特尔计划通过与半导体齿轮制造商ASML的合作伙伴关系来购买市场上的第一个。

英特尔还吸引了半导体行业的其他参与者使用其铸造服务。高通表示,它将与英特尔合作,根据2024年到期的20A流程节点开发芯片。AmazonWeb Services(AWS)计划采用高级包装工具Intel通过其Foundry Arm向客户开放。英特尔此前曾表示,它已经与100多个潜在的Foundry客户进行了讨论。

为了扩大其制造占地面积并赋予铸造客户的“承诺”能力,英特尔此前宣布了计划在亚利桑那州的两个新工厂上花费200亿美元,并在其他地点增加了数十亿美元。

“与我们的客户和生态系统合作伙伴,包括IBM,Cadence,Synopsys和其他合作伙伴,我们将帮助加强国内半导体供应链,并确保美国在研发和高级制造业中保持领导才能。”服务。“我们期待与美国政府进行长期合作。”

英特尔没有共享合同的美元金额。