全球最大的芯片制造装备销售商Applied Materials表示,它引入了一项新技术,该技术可以解决最先进的芯片中的速度瓶颈,为其客户开辟了门,以维持晶体管和其他芯片内部功能的缩放。

The Santa Clara, California-based company said it developed a new way to manufacture wires called contacts—the microscopic canals linking the transistors and interconnects in chips. It also rolled out a new manufacturing tool to reduce the resistance of the contact wires, resulting in a speed boost. Over the last decade, contact resistance has become a bottleneck on improvements to the power, performance, area and cost of advanced chips.

应用材料说,该工具将打开5纳米和3纳米节点的芯片缩放晶体管和其他特征的门,而无需牺牲功率或性能。它上周在年度Semicon West贸易展览会上宣布了这一消息。

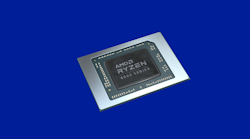

晶体管充当控制电流流动流的微型电子开关,是当今每个逻辑芯片的基础。最先进的芯片具有超过500亿晶体管,可为设备提供计算马力。晶体管被用作芯片神经系统的互连的冠层覆盖。这些微小的电线可以将晶体管相互连接到芯片上的所有其他组件。

A contact is a tiny component that connects a transistor to the interconnect wires wreathed on top of it. The contacts account for more of the overall resistance in chips at the most advanced nodes today. Every contact is more than 1,000 times thinner than a human hair, and a silicon die can be crammed with hundreds of billions of them. According to Applied Materials, that translates to more than 25 miles of contact wires woven into a single wafer.

Today, tens of billions of transistors and interconnects can be crammed onto a single silicon chip. The continuous cramming of these features on chips, called Moore’s Law, has been the electronics industry's playbook for decades, leading to the development of smaller, faster, cheaper and lower-power chips. But the pace of these improvements has slowed as Silicon Valley faces lots of new challenges to continue scaling to 5-nanometers and smaller nodes.

随着这些微小的组件在每个节点上变得越来越小,接触的尺寸也会缩小。这导致触点中有不必要的电阻,减慢连接并限制晶体管的性能。电阻是反对流过接触线的电流。这使其成为每个过程节点上获得的性能和能源效率的瓶颈。

Today, contacts are manufactured by creating a gap—also called the via—in a slab of silicon and then coating the inside of the via with titanium and other materials. Once it is coated, the contact is filled with tungsten, which acts as the conductor. Tungsten is the preferred contact metal for most of the chip industry due to its reduced resistance. The lining on the inside of the contact has higher resistance than tungsten, which slows down the connection.

Applied Materials的半导体业务全球产品经理Zhebo Chen在A中说最近的博客:“考虑涂木栅栏:在涂上一层薄的油漆之前,然后涂上一层底漆,然后是厚实的最后一层。”但是他补充说:“不幸的是,这些制备层变得越来越有问题,因为它们没有扩展。”

The problem is that the lining inside the contact stopped scaling generations ago, leaving less space for the conductor at each node. "The increasing resistance offsets the performance potential of having a greater number of smaller and more advanced transistors, and the issue only becomes worse as the vias continue to shrink at the 5-nm node and beyond," Chen说.

As the diameter of the contact shrinks, the overall resistance increases and performance slows. (Image courtesy of Applied Materials).

As the diameter of the contact shrinks, the overall resistance increases and performance slows. (Image courtesy of Applied Materials).

At the 7-nanometer node, the contact via is only 20-nanometers in diameter, said Applied Materials. The lining on the inside of the contact hogs around 75% of the space, while the remaining 25% of the contact is filled in with tungsten, forming a wire. The problem is that the contacts are becoming smaller at each process node, and as a result the other materials coating the walls of the contact are occupying a larger percentage of the via's volume.

At the 14-nanometer process, an average contact was around 30-nanometers in diameter. At the 10-nanometer node, the features scaled to 25-nanometers, Applied Materials said.

市场研究公司VLSI Research的首席执行官Dan Hutcheson表示,通过堵塞电线并饿死电信号的晶体管,接触墙的材料已经开始类似于“动脉斑块”。他补充说:“我们需要解决“我们需要解决”一些关键的材料工程挑战使2D缩放能够继续。”

应用材料说it has developed a new process to completely fill in the contact with tungsten. By filling 100% of the contact with conductive metal, the Silicon Valley company said its production process lowers the resistance of the wire, speeding up the connections in the chip. That enables electrical current to flow more freely through the contact, according to Applied Materials. The process is sort of like “3D printing at the atomic scale,” Chen said.

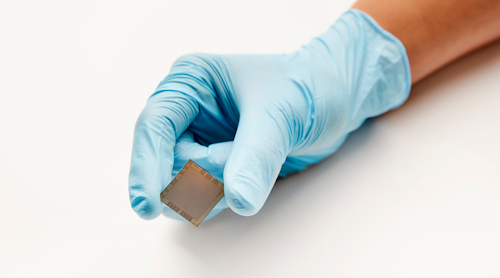

It also introduced a new system called Endura Volta to carry out the process. The new tool handles all steps of the process in a single system, using vacuum-sealed chambers that are even cleaner than the factory's cleanroom to guard against contamination. The tool is used to pretreat a silicon wafer to remove any impurities and then it performs another process to selectively fill the contact, atom by atom, from the bottom up with tungsten.

应用材料说it is capable of filling the contacts without any unwanted voids, seams or delamination, all of which can lead to flaws or cause the contact resistance to rise.

“几十年来,该行业可以依靠2D扩展,以推动电力,性能和地区/成本的同时改进,”其半导体业务产品管理副总裁Kevin Moraes说。“但是今天,几何形状变得如此小,以至于我们正在达到传统材料和材料工程技术的物理极限。”

应用材料sells costly equipment used to carry out all sorts of manufacturing chores in production plants, processing and slicing slabs of silicon into computer chips, memory, and many other types of semiconductors and displays. Applied Materials said the tools it sells are used to manufacture virtually every new chip and advanced display in the world.

但是,英特尔,三星电子和TSMC目前是世界上唯一能够制造出最快,最先进的芯片的公司,用于智能手机可用于超级计算机。

US-based Globalfoundries, which holds the second largest share of the foundry business behind TSMC, halted development of its most advanced chips at 14-nanometers. TSMC, which holds about 50% of the market share in contract chip production, is reportedly on pace to produce 5-nanometer chips by the end of 2020, potentially more than a year ahead of rival technology from Intel, which is facing delays in manufacturing 7-nanometers chips.

应用材料去年投资了超过21亿美元用于研发,该工具目前正在“全球多个领先的客户”中使用该工具。