当使用FPGA进行设计时,可以保证在使用所有可用的单元和寄存器之前用光路由资源。通常你会在设计的关键阶段耗尽资源,此时你需要根据时间表完成开发。

这就是典型的设计周期开始的方式。您接近您的老板,并要求您建立这种复杂但令人难以置信的产品/设计。您提出解决方案,运行少量测试,确实计算计算并使用特定的FPGA创建设计。在原型到达时,您开始编码并具有约25%的FPGA利用率。一切都是根据计划进行的。在我的情况下,它是通过分散收集DMA引擎访问它来处理千兆字节的数据,计算校验和校验和,然后通过DMA将处理的数据放回CPU存储器。我想出的解决方案(图。1)在整个设计中使用32位数据总线访问作为数据媒体。

最初的设计有8对DMA寄存器配置/处理数据处理模块,2 6校验和模块的寄存器,寄存器实用模块,没有调试模块(毕竟,谁还需要调试,你只是打开和一切工作的力量像一个魅力在第一次尝试或所以我想)。

实际上,这种设计花了六个月的努力来充分运作。此时一切都很好,我的FPGA利用率约为50%,在此时,设计率先按计划进行。然后我再次接近BOSS再次告诉我,我们需要更改设计以添加更新字段上的FPGA的功能,开始 - 任意 - 停止数据流,少量其他“次要”。改进。此时,我的寄存器计数的设计跳跃到大约60. FPGA的路由引擎开始需要几个小时才能完成,并且并不总是成功。

|

|

下载本文的。pdf格式 这种文件类型包括高分辨率的图形和原理图(如适用)。 |

当我的设计资源利用率达到80%左右时,FPGA路由引擎因无法满足时序要求而放弃。FPGA中的路由资源对于满足苛刻应用程序的时序需求至关重要,并且是最先耗尽的资源。当资源利用率达到临界水平(70-80%)时,FPGA路由引擎将被迫选择非优化路由,这将增加路由信号的传播延迟。路由引擎的最后一种方法是使用逻辑单元进行路由,此时所有的赌注都无效,通常定时结果会悲惨地失败。

有时FPGA路由引擎只是放弃了一些类似于“由于设计复杂性而不能路由”的消息。这是在通过添加更多功能来扩展我们的设计时发生的。在这种情况下,当我使用不到85%的FPGA时,FPGA路由算法宣告失败。这个问题的强力解决方案很简单;只要选择一个更大的单元数和更多的路由资源的FPGA。但你为“简单的”强力方法所付出的代价是附加在每个生产单位、新图表、新布局和新原型上的额外成本。这在许多层面上都是不可接受的,我决定确定这些失败的根本原因,也许只是改变我的编码风格,以使FPGA路由算法再次愉快。

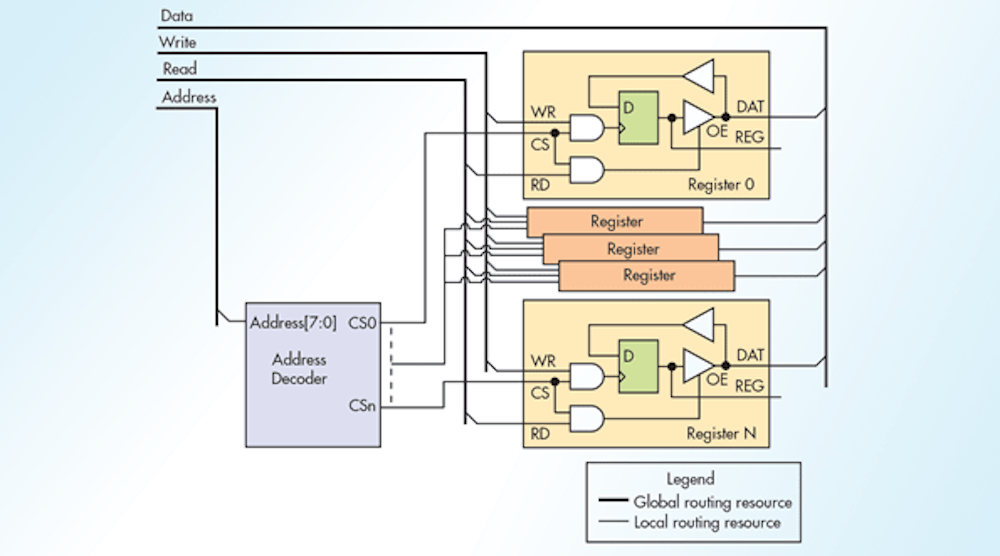

从一开始就显而易见的是,FPGA路由算法在32位数据总线路由上窒息,我的努力分析了该设计区域。我正在采用简单的Tristated总线设计来实现用于配置/访问的寄存器阵列,并在高电平下进行简化编码(图2).这个总线的目标是将寄存器的最大数量限制在256,通过使用8位地址总线来设置。地址解码器正在选择对32位D触发器进行读写操作所需的寄存器。设计中使用REG输出作为本地变量,提供配置/命令接口。乍一看,我们似乎没有使用太多的路由资源,32(数据总线)+ 1(读)+ 1(写)+ 8(地址)或总共42个路由项。我知道FPGA没有内部三态总线,并允许FPGA路由算法将此代码转换为基于复用器的设计。经过更仔细的检查,我发现路由引擎正在映射我的寄存器数组(图3).

请注意,这是理想的情况,当运入时,艰难的路由引擎开始使用本地单元作为路由资源,并且该情况在时序关闭中创造更多的复杂性,但我们将分析理想的解决方案。因此,对于N寄存器,我们将使用32(DIN)+ 32 * n(DOUT)+ 1(读取)+ 1(写入)+ 8(地址)或者我们正在考虑使用1920个路由术语的60个寄存器。在完整地址空间利用率(n = 256)的情况下,我们将使用8202路由术语。

虽然这个数字看起来并不高,但我们应该考虑到FPGA设计通常比图3中描述的寄存器阵列复杂得多,而且大多数路由资源是均匀分布的。因此,如果您的设计/编码使用了一些集中的逻辑,路由资源将在该区域迅速耗尽,结果映射将不适合FPGA,无论路由算法有多好。

我在这个问题上的第一次尝试是通过消除那些巨大的复用器来帮助路由算法。图4显示了我使用大OR门多路DOUT数据总线的方法。这是通过确保在CS未被断言时将DOUT设置为零来实现的。这有助于将图4中复用器中使用的逻辑分解为本地资源。

——通用寄存器- \库IEEE;使用IEEE.std_logic_1164.all;实体gen_reg是通用的(DAT_BITS: natural:= 32;AUTOCLEAR: boolean:= false;AUTOC_VAL: std_logic_vector(31 downto 0):= (others => '1');RST_VALUE: std_logic_vector(31 downto 0):= (others => '0');ADDR_VALUE: std_logic_vector(7 downto 0);ADDR_BITS: natural:= 8);端口(din:在std_logic_vector (DAT_BITS-1 downto 0);dout: out std_logic_vector (DAT_BITS-1 downto 0); rout : out std_logic_vector (DAT_BITS-1 downto 0); addr : in std_logic_vector (ADDR_BITS-1 downto 0); cs : in std_logic; wr : in std_logic; rst : in std_logic; clk : in std_logic); end entity gen_reg; architecture rtl of gen_reg is signal reg_update : std_logic; signal gen_reg0 : std_logic_vector(DAT_BITS - 1 downto 0); signal gen_reg1 : std_logic_vector(DAT_BITS - 1 downto 0); signal gen_reg0_rst : std_logic; signal autoclr_rst : std_logic; signal addressed : std_logic; begin process(clk) begin if(clk'event and clk = '1') then if(gen_reg0_rst = '1') then gen_reg0 <= RST_VALUE(DAT_BITS - 1 downto 0); addressed <= '0'; reg_update <= '0'; else if((addr = ADDR_VALUE) and (cs = '1')) then addressed <= '1'; if(wr = '1') then reg_update <= '1'; gen_reg0 <= din; end if; else addressed <= '0'; reg_update <= '0'; end if; end if; end if; end process; gen_reg_simple: if(AUTOCLEAR = FALSE) generate -- register the value while synchronizing to clk process(clk) begin if(clk'event and clk = '1') then if(rst = '1') then gen_reg1 <= RST_VALUE(DAT_BITS - 1 downto 0); elsif(reg_update = '1') then gen_reg1 <= gen_reg0; end if; end if; end process; gen_reg0_rst <= rst; autoclr_rst <= '0'; end generate; gen_reg_with_autoclear: if(AUTOCLEAR = TRUE) generate -- register the value while synchronizing to clk process(clk) begin if(clk'event and clk = '1') then autoclr_rst <= '0'; if(rst = '1') then gen_reg1 <= RST_VALUE(DAT_BITS - 1 downto 0); elsif(reg_update = '1') then autoclr_rst <= '1'; gen_reg1 <= gen_reg0; else gen_reg1 <= gen_reg1 and AUTOC_VAL(DAT_BITS - 1 downto 0); end if; end if; end process; gen_reg0_rst <= '1' when (rst = '1') or (autoclr_rst = '1') else '0'; end generate; rout <= gen_reg1; dout <= gen_reg1 when (addressed = '1') else (others => '0'); end rtl;

模块gen_reg。vhd(清单1)进行本地地址解码以节省全局路由资源。它有几个参数化的函数来帮助在设计中使用这些代码而无需修改。大多数参数是自解释的,但有一个参数,AUTOCLEAR需要一些澄清。这个功能对于充当事件触发器的寄存器来说是必要的。例如,当我们初始化一个DMA时,命令寄存器的运行位,使用gen_reg实现。一个时钟周期后清除Vhd。这使得设计的操作不用担心,以防我们忘记清除这个位或DMA周期结束之前我们清除它。我们在最终实现中使用这个寄存器设计不变。

这种编码改变了改进的路由算法速度,但不成功解决整体瓶颈。这种设计变化的最终结果是逻辑利用率较少,并加快FPGA路由算法。产生的FPGA图像产生得更快但无法满足时序约束。

很明显,这个问题需要更详细的分析和彻底的设计改变。减少配置寄存器的数量不是一个选择,因为我只是预计随着设计的成熟,它会变得更加复杂。在时域上找到了解决路由问题的方法,更具体的是采用四位SPI来简化路由问题。关键数据路径在图1中用划线标记。我们称其为关键,因为通过这些路径移动的数据量比用于模块配置和访问操作结果的数据量高几个数量级。这为我们提供了以最小的影响设计性能串行化模块通信的机会(图5).

我使用双端口RAM作为配置内存并存储操作的结果。此RAM包含每个模块寄存器具有的所有配置/结果的副本。首先,我们安排了这种配置缓冲区自动刷新,但快速意识到如果我们在软件控件下执行软件会更容易与软件同步。这种方式软件将配置内存并指示SPI主站传输/刷新模块寄存器。在这种情况下,我们正在使用SPI Master的数据路径(4 out和16 in)和使用256x32内存,我们有足够的空间来寻址256寄存器。

这种设计的设计保存了路由资源,并给了我们的房间使用现有的FPGA平台完成设计,并消除重新设计硬件的需要。目前我们正在利用超过85%的FPGA和路线发动机愉快地执行其工作。完成的设计如图6所示。我们在使用四个模块并分配每个模块64寄存器配置空间。我们正在以33MHz运行SPI总线,为我们提供大约62us以传输/镜像此配置空间,而通过关键路径的实际数据传输需要几秒钟才能完成。

这种方法还简化了对FPGA平面图中的每个模块的管理,因为它们中的大多数可以在对路由结果影响最小的情况下四处移动。增加每个模块的复杂性并不会对整体设计产生不利影响,因为复杂性会转化为本地资源的利用率,而在所有FPGA中,本地资源总是充足的。通过提高SPI的运行速度,还有改进设计的空间,但此时每个人都对设计性能感到满意。使用这种设计方法可以使用多达95%的FPGA资源,而无需面对路由算法的激烈竞争。