这篇文章是TechXchange:天线设计101

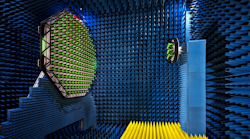

电子束导向是一项相当古老的技术,可以追溯到1905年左右,当时卡尔·布劳恩演示了用相控阵传输无线电波来提高方向性。第二次世界大战期间,早期雷达系统也采用了同样的原理。原则上,相控阵系统采用一系列等间距的天线,通常间隔四分之一波长,利用发射(或接收)信号的建设性和破坏性干扰,产生一个方向矢量。

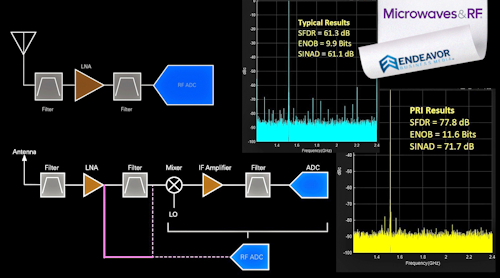

通常,有两种类型的相控阵天线:静态和动态。静态相位阵列天线用于改善传输的方向性和空特定向量,以减少与其他系统的干扰。静态相位阵列天线具有固定干扰图案并导致已知的向量。为了操纵静态相位阵列天线的光束将需要它机械移动。动态相控阵天线使用多种电子方法延迟RF信号的到达或将发射的阶段移位天线元件。这两种方法都会导致形成可预测的传输或接收向量的模式(图1).

电子光束通过机械方法具有许多优点。电子转向可以比机械天线更快地扫描,允许诸如高级雷达等系统同时跟踪和搜索。另一个优点是能够动态地改变扫描模式。通过将伪随机模式施加到扫掠载体,军用雷达可以通过去除可预测的发射模式(例如,给定的扫描时段)来避免对策。

电子战(EW)接收机,也被称为早期预警探测接收机,使用与相控阵雷达系统类似的概念。这些接收器被设计用来指示威胁矢量给操作员和飞行员,以避免探测或直接的威胁,如导弹防御系统。

这些电子战接收器使用几种方法中的一种,通过到达角(AoA)来检测威胁。电子战天线系统可以通过幅值比较来实现面向对象的天线分析,即通过比较各天线单元的相对功率电平来计算辐射源的矢量。这些系统也可以使用到达时间差(DTOA)或其他基于干涉测量的方法。

此外,由于可用的通信频谱也在减少,动态波束导向的使用也被用于空间复用的下一代蜂窝基础设施,以及在高级Wi-Fi热点等系统中发现的自适应波束形成。这允许运营商通过分配空间向量以及编码或频率分配来有效地多次“耕种土地”,这为增加用户提供了另一种方法。

Phase-Coherency要求

随着用于直接射频采样的超高速数据转换器和组件的出现,工程师们已经开始移除早期雷达和其他动态导向相控阵中使用的复杂移相系统。数据转换器被移到更靠近每个元素的位置,提供了极大的灵活性。这同样适用于电子战和无线基础设施系统。

它的一个优点是能够在失败后慢慢降级。例如,在一个只有有限数量的数据转换器和移相器的系统中,一个转换器的故障可能会极大地降低系统的有效性。然而,如果每个元素都有独立的转换器,那么单个通道的损失将不会显著影响系统性能。另一个优点是能够根据任务或负载重新配置阵列的部分和动态配置系统。

所有这些能力都依赖于射频信号(包括接收和发送)的确定性采样,它提供了必要的相位信息。当数据转换通道数量有限时,这就不那么复杂了。然而,随着行业转向基本波束形成,对所有数据转换器进行相位对齐的挑战变得越来越困难。

数据转换器和确定性延迟

工程师可以使用几种技术来通过采样系统的元件建立已知的延迟。通常,每个通道可以具有固定和可重复的延迟,也称为确定性延迟,或者架构必须提供校准的方法和系统中固有的相位误差。此外,设计人员可以选择提供两种方法,这可以减少上电时的校准时间。

当模数转换器(ADC)通道采样输入时,器件的轨道和保持部分锁定采样时间的输入电平,这允许ADC电路将该模拟样本转换为数字位。当样本被锁定到输出位可用时,所有转换器将在锁定到输出位时的某些延迟。在基于多转换器的系统中,在采样时钟或输入信号路由的布局上的微小变化可能会在不同通道之间引入一些延迟差异。很多时候,这可以校准,因为这些延迟是由设计确定的。

然而,许多现代超高速数据转换器使用方法可以不相对于具有固定延迟的采样时间提供输出数据。这可能是由于转换器架构,用于生成时钟的内部锁相环(PLL)的相位误差以及数据序列化方法。这适用于在发射器(或雷达激励器)中使用的接收链和数模转换器(DAC)中使用的两个ADC。

建立相位相干性

现代射频系统中实现的绝大多数超高速数据转换器都已不再使用并行接口,而是迁移到串行数据上。这主要是由于需要大量的平行传输线来传输数字数据。

例如,ADC12D1600是3.2-gsample / s,12位ADC,需要96个电匹配的传输线(48对),加上时钟对被路由到FPGA或ASIC。相比之下,ADC12J4000,采用4.0 gsample /s 12位转换器JESD204B串行接口,只需要16个传输线(8对)和两个额外的时钟对在一个10 × 10毫米的封装。

当数据被序列化时,将时钟嵌入到流中,从而消除要求将时钟的电长与数据线匹配。然而,由于帧或传输开销(例如8b / 10b编码),数据速率可能不会被锁定到采样时钟。另一个不匹配源可能是由于从数据转换器(PCB)上的数据转换器的位置和处理元件(例如FPGA)的位置而导致的数据通道不匹配引起的延迟。这些不确定性可能导致实际采样数据在不同时间到达处理器或FPGA,这在相干系统中是不可接受的。

提供确定的延迟

可以使用几种提供确定性延迟的方法来解决这些问题。JESD204B接口标准引入了子类,以提供与旧版本的向后兼容性,并包括一种新的方法来建立数据转换设备之间的相位一致性。

如前所述,这个接口可以比ADC或DAC的单个通道运行得更快。一旦数据被反序列化(例如,返回到处理元素中的并行数据),这种速度就会产生样本实际获取时间的不确定性。

JESD240B子类1和子类2都提供了一种方法,可以在位于电路卡组件(CCA)上的单个数据转换设备之间建立确定的延迟。虽然每种模式都需要匹配设备和系统参考时钟,但它们放松了匹配数据通道的需要,而数据通道是PCB轨迹的主要部分。

当CCAs数量较多时,可以通过匹配的传输线或介质(如同轴电缆)向所有板提供一个低相位噪声主RF时钟。在许多时钟发生器中,如LMK04828,有一些机制来调整这些主时钟的相位,以“调出”主时钟源和每个CCA之间的任何不匹配(图2).

每个JESD204B接收器块具有弹性缓冲器,允许车道不匹配。在初始化过程中,通过接收方块确定最大延迟。接下来,相对于本地时钟(局部多帧时钟或LMFC)选择点,以允许所有通道以相位释放。这保证了所有样品对齐和相干。

另一种方法不需要任何形式的已知时钟之间的延迟,但可能需要一个相当深的数据缓冲区,并使用实时校准。这可以通过两种主要方式来实现。首先,从一个电源周期到下一个电源周期的延迟可能不一致,因此必须在每次系统通电时,或者当JEDS204B链路丢失并重新建立时进行校准。

需要一种机制来切换到外部校准脉冲,它为每个通道连贯地到达(或通过一个已知和固定的延迟)。在这种模式下,系统可以查找校准脉冲,确定样品之间存在多少差异,并调整每个转换器通道的缓冲释放点。这可以与子类1或子类2结合,以减少校准相位不确定性所需的时间。

第二种主要方法是使用时间戳。现代许多高性能数据转换器,如ADC12J2700,有一个时间戳输入。当启用该模式时,时间戳输入与模拟输入同时采样。时间戳输入的状态被放置在最低有效位(LSB)中,有效地减少了转换器的动态范围1位(约6.02 db)。

将校准脉冲放置在时间戳输入上可以实现相同的相位调整方法,但不需要注入校准脉冲所需的RF输入开关。它极大地简化了校准电子学,实际上提供了一种数字手段来对转换器进行相位校准。

结论

随着动态相控阵天线系统利用超高速数据转换器的可用性来提高灵活性和性能,在大量数据转换器之间保持相位相干的需求是一个不断增加的挑战。随着JESD204B接口标准的引入,为设计者提供了建立确定性延迟的机制。这些方法单独或与各种时间戳和校准方法相结合,可以在大量数据转换器上提供系统范围的相位相干性。

阅读更多文章TechXchange:天线设计101

参考:

数据表:ADC12D1600,ADC12J4000,ADC12J2700,LMK04828.

JEDS204B接口。