Tabula'sAbax FPGA实现了独特的3D时空体系结构(请参阅FPGA输入第三维)基于时间的系统以序列激活的逻辑层实现FPGA。从本质上讲,这将硬件量乘以设计所用的层数。

最新的公告是发行Tabula的手写笔开发平台。它提供了常规FPGA设计流(图1)差异与对设计师有效透明的时空体系结构无关。相反,该工具的显着特征是它是基于网络(图2)。

我有机会退房手写笔(图3)。It actually runs on a Linux platform on Tabula's development site and is accessed using VNC (Virtual Computing Network). VNC is the typical remote control platform on a Linux system and works on most operating systems like Windows.

这种方法有许多优势。首先,启动成本很小。其次,实际上没有必要设置,因为VNC甚至可以通过Web浏览器使用。第三,技术支持始终在场,可以在帮助开发人员时共享控制台。最后,该软件将始终是最新的。

有可能出现的问题,因为设计files are located on the server. Uploading, downloading and backups can be an issue. Customers have access to their files. A high speed Internet connection is a requirement but not a problem given the general availability of this type of support. Security for this type of configuration may be an issue for some customers but so far Tabula has found quite a few that like the set up.

手写笔涉及RTL,VHDL,Verilog和System Verilog。它提供了一个针对Abax FPGA的位置和路由编译器。可以在时空支持方面检查结果。这更多的是信息,因为从执行角度来看,Abax FPGA的作用像常规FPGA。

时空分层的实际控制由通常是系统设计的一部分的定时约束控制。可以调整这些约束以更改所得的配置,但我发现简单地忽略了时空分层体系结构很容易。

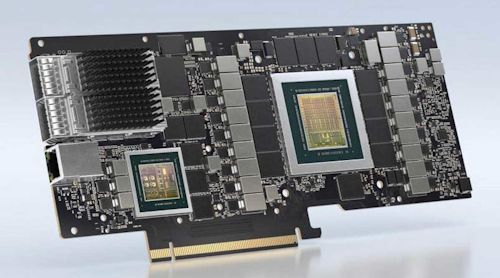

结果项目可以下载到Tabula的7500美元之类的平台上Abax开发委员会(图4)。我没有方便的,所以我只能享受显示时空布局的结果分析文件。董事会展示了Abax功能,例如PCI-Express Gen1/Gen2,以太网10/100/1000/10000,DDR3支持甚至V1 Coldfire支持。

使用手写笔几乎所有熟悉FPGA开发工具的开发人员都可以轻松自在。手写笔是完整的,因此除了能够将现有设计带入手写笔外,还可以从基础上构建设计。

我没有尝试的一件事是片上调试支持。这显然需要芯片来尝试一下。我听说它与Xilinx和Altera开发平台中发现的类似设施相当。