一位工程师在系统中测试一个原型电路时,遇到了一个看似奇怪的现象,他向我寻求帮助。他在发射器的输出端看到了信号的“神秘”剪限失真。他告诉我,他用比实际负载重得多(小值)的电阻负载检查了这个跟随者,但没有看到任何可见的扭曲。然而,当他把原型板连接到系统上时,信号的底部出现了明显的剪切。

看原理图,我看到下一个器件的电阻输入被一个大电容从跟随器中解耦。我向他解释了这个问题的原因。我还意识到,与电阻负载不同,当剪切的可能性相当明显时,电容耦合电阻负载的问题很容易在设计期间被忽略。

|

|

下载。pdf格式的本文 该文件类型包括高分辨率的图形和原理图。 |

一个单晶体管发射极跟随器可以在其晶体管的限制内,为负载提供足够多的电流。然而,晶体管不能吸收电流。当从动件交流耦合到电阻负载时,这可能会导致输出信号的削波失真,原因有时并不明显。

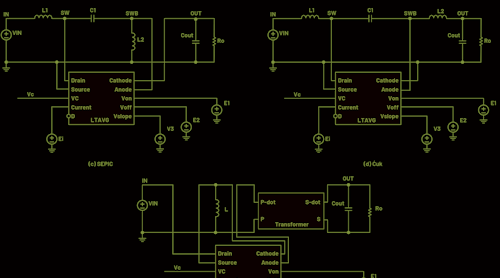

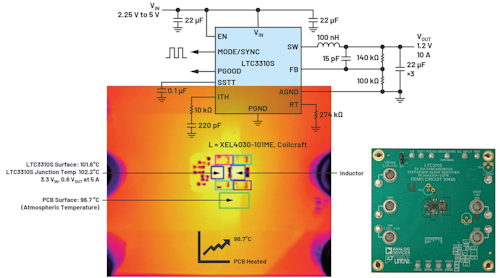

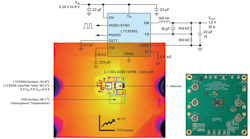

首先,看一下简单的NPN发射器跟踪器(图1)以及可能出现的明显剪切变形。正向剪切到VCC如果一个大的输入信号超过V,输出将会发生CC大约0.7 V,打开晶体管Q1的基极集电极结(这里,一个普通的2N2222)。这个结的工作原理就像一个在限幅点以上的二极管,将输入信号分流到VCC.如果这个二极管的电流不受输入电阻R的适当值的限制我时,晶体管可能损坏。

负削波发生在输入信号的负摆动期间,如果在晶体管的基础上的输入电平变成小于约0.7 V (V是晶体管)。在这种情况下,晶体管的基极-发射极结成为反向偏置,其发射极电流(IE)降到零,晶体管关闭。这将导致输出信号在其底部剪切为零,直到输入信号将晶体管返回到正常模式。

靠近限流点,发射器电流IE,且从动件增加其总谐波失真(THD)水平。在正弦输入信号的情况下,为了防止这种明显的削波:

V从- - - - - - VAMPL- - - - - - V是> 0 (1)

在VAMPL是峰值振幅和V从为正弦波输入源的直流偏置电压。

描述的削波是用PSpice电路的瞬态分析,与交流输入源设置为VAMPL= 2 v, v从= 2.3 V和频率为1 kHz。在这种情况下,VI_MIN= 0.3 V,瞬态分析显示输出信号的底部有一个削波(图1 b).

图1c为与V相同电路仿真的结果从= 4 V,这给了一个1.3 V的边缘高于剪辑水平。现在暂态分析并没有显示输出信号的剪切和其他明显的失真。此外,模拟剖面中的傅里叶分析显示输出文件中的THD为0.143%。

增加从动件的负载产生类似的结果。例如,即使是RE= 0.5 kΩ在图2a的电路中(这是R的三分之一E,图中没有明显的变化,THD仅从0.143%略微增加到0.145%。

接下来,连接交流耦合负载电阻Rl追随者。去耦电容C1的值选择足够大(1.0 F),以避免在瞬态过程结束时输出信号可能出现失真。乍一看,你会希望得到与图1中电路相同的模拟结果,但在R上没有直流元件l.不过,暂态分析(图2 b)显示输出信号和晶体管发射极的显著剪切。

对于这个不明显的结果,有一个简单的解释。在稳定状态下,C1被充电到Q1发射器的直流电平。在V的正半循环中在, Q1的发射器电流分裂到RE和Rl(我再保险和我RL分别).发射极电流I的最大电平E_MAX是:

我E_MAX= [(VAMPL+ V从- - - - - - V是) / RE) + (VAMPL/ Rl)

然而,在V的负半周期在,而我再保险仍然从晶体管Q1中定向出去,从而降低了它的值,IRL回到Q1,然后从I中减去再保险.

我E_MIN= [(V从- - - - - - VAMPL- - - - - - V是) / RE] - (VAMPL/ Rl)

如果这个减法的结果是负的,IE_MIN当降至零时,输出信号会受到剪断。

我之所以RL返回到Q1也不明显。在稳定状态下,C1充满电。它左边的直流电压是VE,高于最小交流信号时的绝对电压(VAC_AMPL= 2 V),在这种情况下相当于4 - 0.7 = 3.3 V。电容器的直流电平在右侧为零。

因此,在交流信号的负循环过程中,通过R的电压E跟随输入信号的负波,但由于偏置总是正的。RE组合电流中的分量等于Q1/R的发射极电压E> 0。输出电压VO在R的顶端l也跟随输入信号的负波,但它的直流偏置为零。负波也是负的。在这个区域,它从0变到- VAMPL,导致电流通过Rl向相反的方向走。我RL总是小于0。

为了防止剪切问题,我E_MIN应该总是大于零:

我E_MIN= [(V从- - - - - - VAMPL- 0.7) / RE] - (VAMPL/ Rl) > 0

或

[(V从- - - - - - VAMPL- 0.7) / RE) > VAMPL/ Rl(2)

|

|

下载。pdf格式的本文 该文件类型包括高分辨率的图形和原理图。 |

因此,为了避免在交流耦合电阻负载的单晶体管发射器跟随器中发生剪断,方程2中的三个变量应符合以下约束条件:

VAMPL_MAX= (V从- 0.7) × [rl/ (Rl+ RE)]

或

VOFF_MIN= VAMPL((RE/ Rl) + 1] + 0.7

或

RL_MIN= [VAMPL/ (V从- - - - - - VAMPL- 0.7)] × rE

同时,从方程1:

V从- - - - - - VAMPL- 0.7 > 0。

参考文献:

1.Alan b . Grebene双极和MOS模拟集成电路设计, Wiley - Interscience Publications, John Wiley & Sons。

2.道格拉斯的自我,小信号音频设计,中央新闻台,2010年。

3.P.霍维茨,温菲尔德希尔;电子艺术,第二版,剑桥大学出版社,1989年。