采用高性能模数转换器(ADC)的设计人员有一个共同的问题:市场上很少(如果有的话)的放大器能够提供缓冲输入信号所需的精度,并在不损失性能的情况下驱动16位ADC。10-V全尺寸ADC必须能够分解150µV。这是一个艰巨的任务,即使输入频率低至100 kHz。

更复杂的是,如今许多adc的全量程均为5v。任何用于驱动这种设备的缓冲区必须贡献不超过75µV的错误,否则系统性能将受到损害。这种低噪声和低失真的要求确保了有限带宽放大器(如fT= 30mhz)根本无法实现这样的性能。

总误差=均方根(噪声、失真、CMRR、增益误差)< 75µV

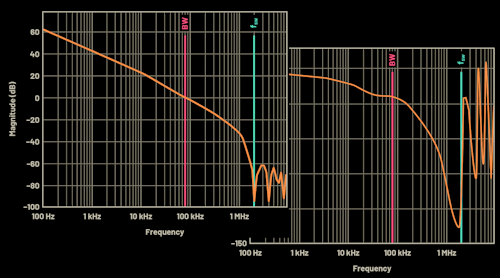

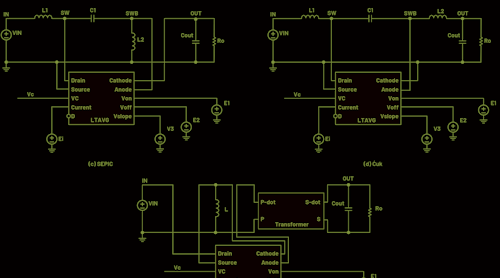

该设备改进了最先进的电路约20分贝目前可用的缓冲器(图1).两个放大器组成这个系统。所述第二放大器包含在所述第一放大器的反馈回路中,并配置为增益为1。

请注意,V出近似等于V在.TP2处的电压类似于V在也因此,第一放大器的非反相端子与反相端子之间的误差与第二放大器的非反相端子与反相端子之间的误差相同。因此:

V出= V在+ VERROR1−VERROR2

或

V出= V在

图2显示了该电路在0- 2.5 v正弦波输入10 kHz时的性能。当比较误差(V出−V在)在底部跟踪到单独的缓冲区(V出−VTP2),可以观察到明显的误差减少。图3在±10-V的三角形波形输入1khz时也有类似的改善。放大器带宽被设定为30兆赫兹。