您将学到什么:

- Characteristics of transceivers that combine analog, digital, and mixed-signal components, such as SDR, RFSoC/SoC, and DFE technologies.

- Basics of an SDR and RFSoC/SoC.

- The advantages/disadvantages of using an SDR with discrete integrated circuits and other components versus a RFSoC/SoC.

Transceiver devices are ubiquitous in today’s highly connected world. Various transceivers exist for a wide range of applicability, which often combine analog, digital, and mixed-signal components. This article focuses on software-defined radio (SDR), radio-frequency system-on-chip (RFSoC/SoC), and digital front-end (DFE) technologies, all of which work as transceiver devices with embedded digital-signal-processing (DSP) capabilities.

讨论的是与RFSOC/SOC(或其他完全嵌入的无线电前端)相比,使用SDR与离散的集成电路(IC)和其他组件的优势/缺点。

Basics of SDR

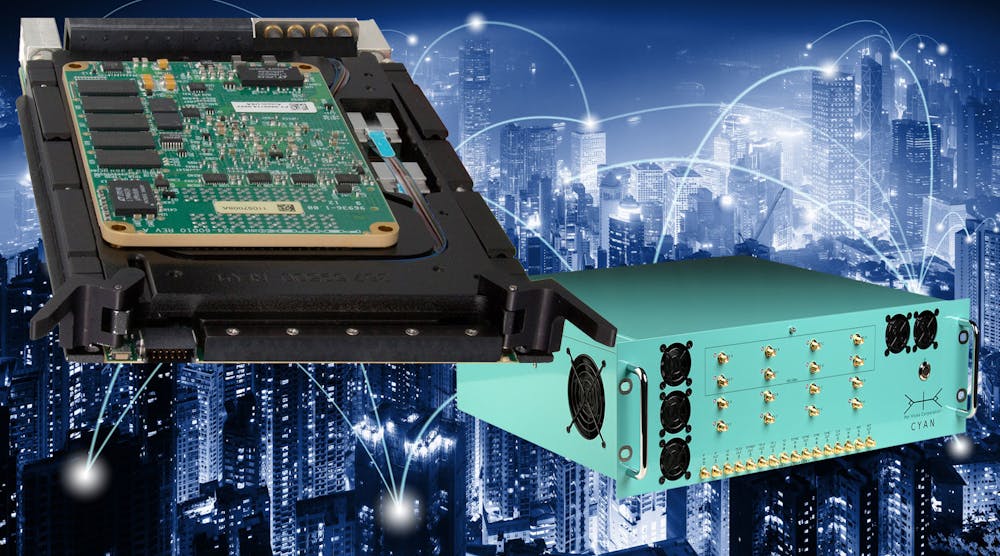

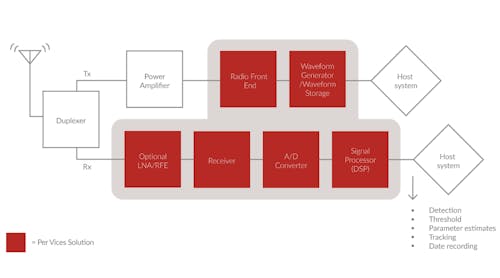

An SDR is a highly flexible transceiver platform consisting primarily of a radio front end (RFE), mixed-signal interfaces, and processing support in the digital backend(图。1). High-performance SDRs are critical for many wireless applications and tend to have more analog circuitry and are more easily integrated into RF systems compared to the RFSoC/DFE transceivers we’re discussing.

SDR本身包含一个带有接收(RX)和传输(TX)功能的RFE,以在广泛的调音范围内处理信号,该信号使用模拟和数字中的各种混合阶段来完成。此外,这些无线电连锁链的带宽非常高,每个无线电链最多3 GHz,每SDR最多可达16个完全独立的无线电链。

The SDR’s digital backend contains a high-performance Arm CPU/FPGA with onboard DSP capabilities for modulation, demodulation, digital upconversion (DUC), digital downconversion (DDC), filtering, etc. Furthermore, SDRs are highly reconfigurable and upgradable to the latest radio protocols, DSP algorithms, IP cores, etc.

FPGA还包含将数据包装到以太网数据包中的手段,并在10至100-GB/s链接上通过SFP+/QSFP+链接运输。这些设备带有API,可通过主机系统开发/控制无线电系统,以及信号处理开发工具包,例如GNU无线电。

RFSOC的基础知识

Traditional system-on-chip (SoC) technologies were designed specifically for their use case, such as Bluetooth, Zigbee, Wi-Fi, and even mobile phone chips (GPS, etc.), all of which were reduced to a small-scale transceiver design. As with most electronics, size has decreased while functionality is on the rise, as can be seen in one of the latest developments in transceivers—the RF system-on-chip (RFSoC). These transceivers or fully integrated SoC dedicated chips were developed by Xilinx and premiered in 2017.

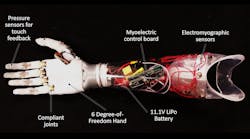

In particular, RFSoC devices essentially embed RF-class multichannel analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) with Xilinx’s multiprocessor system-on-chip (MPSoC) as well as an Arm processor enhanced FPGA. As shown inFigure 2, the architecture integrates the mixed-signal’s interface (ADC/DAC) into the signal chain. These devices use a direct sampling ADC/DAC with DDC and DUC.

Pros and Cons of RFSoCs

A significant benefit of RFSoCs is their lower power consumption. The driving factor behind the reduced power of RFSoCs is the need for fewer boards, and the elimination of the interfaces required to connect the various ICs in a discrete solution.

One such common serial interface standard is JESD204B, which has been eliminated from the Xilinx RFSoC product line. With the RFSoC, data converters are integrated directly into the FPGA using parallel interfaces, and thus, these devices don't require the high-pin-count external connections needed for discrete parallel interface converters.

此外,RFSOC没有与JESD204串行接口相关的延迟。这使它们成为低功率,多通道计数和低延迟应用的有吸引力的解决方案。成本效益也是SOC收发器在需要有限功能的应用中的好处,如上所述,该功能已集成在单个芯片上。在这些应用中,RFSOC设备仅需要几个支撑电路,例如用于控制的微处理器,电源和天线。

While RFSoC devices are impressive and can be advantageous in a number of applications, they also have multiple disadvantages. As RFSoCs/DFEs are essentially chips with embedded direct-sampling data converters, an engineer often needs to design a printed circuit board (PCB) around the RFSoC to increase capabilities as well as house the boards in some sort of enclosure (for environmental or ruggedization, for instance). Such a dense design of data converter interfaces creates many challenges.

对于初学者来说,在RFSOC上表明完整性时存在许多问题,包括虚假的数字信号拾音器,频道之间的串扰,与阻抗匹配有关的问题以及热管理问题。无法避免其中的大部分,尤其是在这些效果更可见的较高频率下。这就是为什么当前市场上最复杂的RFSOC只能调整高达7.1 GHz的原因。

此外,新的板组件(PLL,NCO,LOS等)之间的时序和同步都需要与RFSOC集成,在此,仅在数字域中考虑时序/对齐方式。但是,必须设计PCB布局以考虑RFSOC的延迟要求。

Many challenges also crop up when developing the FPGA “firmware” code for the RFSoC/SoC/DFEs, because you need to be widely familiar with programming in hardware descriptive language (HDL), plus various other embedded-system design programming, to have a functional radio/DSP system. For instance, if you’re trying to design a custom modem, implement some sort of packetization standard (i.e., to transfer data over Ethernet in VITA 49 packets), or develop a custom signal processor, a lot of development time will be required.

Pros and Cons of SDRs

从关于RFSOC的讨论中可以收集,通常需要进行大量开发才能启动和运行功能性的无线技术。因此,已经开发的SDR(即具有API,与DSP开发工具包一起使用,已经将数据从收发器传递到主机系统计算机/存储设备,使用VITA 49数据包格式等)可以显着降低时间。进行市场或设置特定应用程序。

对于使用专用Analog RFE的SDR制造商,仍有可能建立需要许多性能优势的定制设计。当您使用离散的商业现成(COTS)IC(放大器,过滤器,衰减器,调音台等)建立整个无线电链时,具有很大的灵活性,可以针对特定的RF性能要求进行优化。

For instance, the RFE can be customized for various performance requirements (tuning range, elimination of spurs within a band, output power, etc.). Another advantage of using an SDR with discrete components is that you can bypass numerous components in the RFE, which isn’t possible with RFSoCs. On top of that, the SDR’s RFE allows for higher tuning ranges (due to multiple mixer stages/multiple RFE signal chains). And in certain applications, it’s often possible to design an SDR that conforms to a particular size, weight, and power (SWaP) specification.

In terms of FPGA resources, on high-performance SDRs like每个恶习Cyan platform, feature many more logic elements/cells. These SDRs contain 5.5 million logic elements compared to the maximum of 930,000 currently available on RFSoC. Also, when working with an SDR manufacturer, it becomes possible to implement custom HDL code in a much less time-consuming and cost-effective manner compared to having to develop in-house.

The ease of use is worth mentioning, too. With most SDRs, data from the FPGA is passed over qSFP+ ports to a host system that has a number of different UIs to control the actual radio (for instance, with GNU Radio, Web UIs) and maintains compatibility with UHD for development in C++, GNU Radio, or Python.

Thus, when using or integrating an SDR into a wireless system, you’re able to focus on developing your application on it, rather than working out how to make the device operate as a radio device in the first place. In fact, many manufacturers of SDRs use SoCs in their digital backend and develop their analog RFE and other PCBs and APIs around these.

Of course, SDRs do come with some disadvantages. For one, these devices tend to be more expensive than many RFSoC/SoC DFEs. Moreover, high-end SDR devices often use larger FPGAs and JESD transceivers between data converters, and thus consume considerable power (albeit, this can be optimized for various requirements). Another disadvantage of some SDRs is the size/form factors of such devices. While it’s possible to make custom chassis/form factors for an SDR, these are generally much larger than small-form-factor RFSoCs/SoCs.

Suitable Applications for Each Transceiver Type

RFSoCs目前正在销售工作4G/5G base station equipment and other small-form-factor/low power consumption wireless systems. 5G base stations are often good applications of RFSoCs, particularly in remote radio head units (RRUs) in small-cell deployment due to the need for a very small form factor. Other applications include LiDAR for autonomous-vehicle technologies, as well as unmanned aerial vehicles (UAVs)/unmanned underwater vehicles (UUVs) that require low-power wireless communications.

另一方面,对于宽这个特别提款权是有用的taneous-bandwidth (IBW) applications, such as spectrum monitoring and recording, which can be combined with storage and playback solutions(图3). In addition, for a large swath of radar and satellite communications in higher frequencies, such as Ka- or Ku-bands, the higher tuning range of an SDR often is necessary.

The analog RFE also is much better suited for applications requiring better wide-band dynamic range and/or spurious-free dynamic range (SFDR), such as in electronic-warfare (EW)/SIGINT applications. And when it comes to easier prototyping, SDRs likely are the better option, due to their ease of use with platforms such as GNU Radio and other DSP toolkits. They allow for much easier modification/redesign thanks to their simple interface, compared to having to develop a custom API or HDL code when using an RFSoC.

Conclusion

RFSOC,DFES,SDR,收发器 - 这些设备的众多名称基本相同:传输和接收信号。这些设备有许多优势和缺点。此外,您的应用程序将决定您在开发上花费多少时间/金钱和资源以及此类应用程序的交换要求。如所讨论的,高性能的SDR和RFSOC截然不同,每个人都有其优点和缺点。