随着数据转换电路多年来的加速,目前的串行接口一直跟不上。但是现在有了一个新的接口,叫做JESD204C。它是JESD接口标准的下一个迭代。本文介绍了JESD204C,解释了它的特性和优点,并强调了它与其前身JESD204B的区别。

赞助资源:

JESD是什么?

JESD204C是联合电子器件工程委员会(JEDEC)的标准。它是一个高速接口,用于连接快速模数转换器(adc)和数模转换器(dac)到高速处理器、fpga和asic。

该标准首次出现于2006年,提供3.125 gb /s的数据速率。随后的版本在功能和速度方面进行了改进。2008年的JESD204A版本增加了车道同步,使多个串行车道与多个转换器保持一致。JESD204B在2011年的升级将速度提高到12.5 Gb/s,并包含了确定性延迟。与新的JESD204C版本,接口数据速率跃升至32.5 Gb/s,以及其他改进。顺便说一下,该标准的新版本与以前的版本保持了一些向后兼容性。

年复一年,adc和dac在速度方面继续挑战极限。千兆位速率很常见。而那些传输或接收高速数据的电路,如fpga或快速微处理器,已经能够匹配这些永久的速度增长。

然而,限制因素围绕着这些设备的互连。

之前的JESD204B标准被广泛使用,以允许这些快速电路相互通信。数据交换发生在PCB、背板上的芯片之间,以及仪器或其他设备中模块或组件之间的短电缆之间。但正如一些人已经发现的那样,JESD204B规范不再适合于连接最快的数据转换电路。现在,JESD204C使接口跟上了速度。

应用程序

JESD204C接口几乎可以适用于任何数据转换器运行在高兆位和千兆数据速率下的设计。应用程序的样本包括:

- 测试仪器

- 5 g移动设备

- 其他蜂窝基站设备

- 医疗器械

- 军事/电子战(EW)

- 卫星

- 几乎所有直接转换软件定义无线电(SDR)

JESD204B和JESD204C比较

的JESD204B标准是一个真正的突破,并被广泛采用。它提供了12.5 gb /s的数据速率,多车道支持和同步,8B/10B编码和确定的延迟。JESD204C标准拥有其前身的所有特性,并增加了一些新的优点,如32.5 gb /s的数据速率、64B/66B编码和确定性延迟。

该标准的关键部分是64B/66B编码。它还支持64B/80B编码选项。在早期的B版标准中使用的编码方法是8B/10B,这意味着每一个要传输的8位先转换成一个唯一的10位数字。这样的编码有几个很好的理由:

- 编码后的字符现在包含更多的位和位转换,这些位和位转换有助于时钟恢复和数据流的对齐。

- 这种编码确保直线上的平均dc是恒定的。比特的随机数会导致传输路径上直流平均值的变化或徘徊,从而引入比特错误并导致其他恼人的操作特性。

虽然8B/10B编码是有益的,但它也降低了传输速度。传输10位,而不是8位,所以需要更长的时间。当数据速率(R)仍然基于比特时间(t)时,净数据速率减少了20% (R = 1/t)。

JESD204C标准使用64B/66B编码。它不仅改善了直流平衡、时钟恢复和数据对齐,而且比特开销更小,为3.125%,大大低于8B/10B方法。

所述信号处理包括编码前的扰频器。扰码器是一种数字电路,它处理串行数据以创建一个高度随机化的版本。像循环冗余校验(CRC)一样,它使用基于多项式的算法过程,在本例中是1 + x14+ x15.置乱的最终效果是一个具有频谱的串行数字信号,可以大大降低电磁干扰的产生。

确定的延迟

决定论是指能够预测或决定某些行为何时会发生的特性。与决定论相反的是随机性。确定性的东西可以精确和可重复性地预测操作何时会发生。

延迟是指在操作开始和结束之间发生的时间延迟。延迟通常是电子操作发生或信号从系统的一个部分传播到另一个部分所需要的总时间。延迟以秒或时钟周期来衡量。

两者的结合对该设备或设备的实际性能至关重要。例如有两个或更多数据转换器的设备,用于I和Q转换。交错转换器是另一个例子。当多个输入或输出必须相参时,JESD204C标准可以提供这种条件。为了在大多数系统中进行正确的操作,所产生的确定性延迟必须是恒定的和可重复的。

ADC的延时是指从捕获模拟样本到ADC进行后续处理,再到出现数字输出之间的时间。DAC的延时也类似——从数字输入到DAC电路到相应的模拟信号首次出现之间的时间。这个延迟以秒或时钟周期数来衡量。

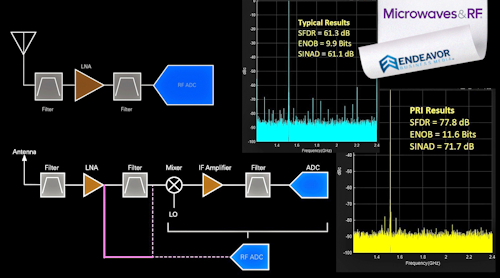

确定性延迟通常定义为从发送端输入数据到接收端输出数据之间的时间。它不包括ADC和DAC延迟(见图).ADC将信号处理成要传输的数据帧。发射机(TX)电路处理包括置乱、8B/10B或64B/66B编码和一些数据对齐。数据通过串行链路传输,可能与与多个adc相关的其他串行链路并行。

在接收端(RX),信号被解码和同步,然后解调。缓冲存储器用于在需要时提供一些时间调整。请注意,总链接延迟必须一致,以实现确定性延迟。

在大多数高速应用程序中,来自多个流的数据必须以一致的已知延迟通过系统。该标准定义了一些实现这一目标的信号。不同的信号和时钟有助于实现车道同步、车道对齐和错误检测。

主时钟是数据帧时钟和LMFC (Local Multi-Frame clock)。SYSREF和SYNC信号用于提供时间基准对准。SYNC是一个接收到发送的信号,用于同步请求和错误报告。SYSREF信号是影响LMFC的相位定时参考。

赞助资源: