由斯Velivala

修路是一个多阶段的过程。您必须选择路线,清除任何障碍,并平整地面之前,您可以应用铺路。制造一个集成电路(IC)芯片也是如此。设计团队使用地点和路线(P&R)工具来实现布局,设计规则检查(DRC)以消除施工障碍(错误),并优化制造设计(DFM),以最大限度地提高制造能力和性能。当然,这是对这两个过程的高度简化(但通常是准确的)的看法。

这两者所固有的挑战是用尽可能少的资源在最短的时间内取得预期的结果。克服这个挑战通常意味着找到新的更好的方法来完成整个过程的步骤。

P&R工具在RTL中执行设计描述的自动化实现。也就是说,他们创建了一个物理布局,将设计师提出的功能转换为互连、设备、层等等。然后,P&R工程师必须使用DRC根据设计规则评估布局,以发现和修复任何错误。

铸造厂为每个工艺制定设计规则。在每个新节点上,设计规则的数量增加,每个规则的复杂性也增加。几年前,为了简化和加快DRC过程,提供P&R工具的电子设计自动化(EDA)公司开始在一组基本的DRC检查中进行构建。P&R工程师在P&R工具中运行这个原生的P&R DRC,以查找和修复布局中的大部分DRC错误。

然而,这个原生的P&R DRC功能并不是为了取代诸如西门子EDA的Calibre nmDRC平台等工具所提供的结束DRC验证而设计的。这些审批DRC工具与包含节点完整设计规则集的DRC规则组一起工作,并且已被铸造厂认证,以通知设计不存在会影响其可制造性的错误。

当P&R工程师达到P&R DRC所能做的极限时,他们必须对布局运行signoff DRC,以发现和修复那些P&R DRC无法处理的错误。这意味着将P&R和IP数据合并到单个数据库中,将该数据库输出到GDSII/OASIS,执行一个批处理结束DRC运行,检查和调试错误,并应用修复程序。哦,然后一遍又一遍地做这整件事来确认修复。

由于流输出和批处理DRC都非常耗时和资源密集型,这些迭代可能会吞噬宝贵的调度时间,以及人力和计算资源。听起来这就是你移除道路上障碍物的时候了……

EDA公司就是这么做的。在过去的几年中,已经引入了一些创新功能,使P&R工程师能够从他们的P&R环境中访问质量优异的DRC。没有流线,没有批量DRC运行。我们将使用Calibre RealTime数字接口从西门子EDA向您展示一个例子,如何这个功能的工作。

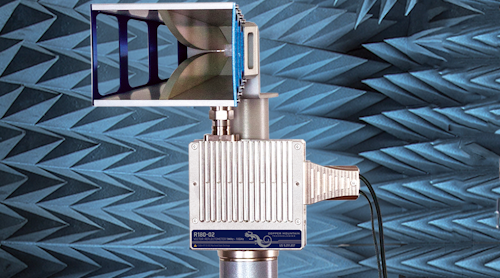

Calibre RealTime Digital接口集成了所有主要的P&R工具直接调用Calibre分析引擎运行铸造厂合格的签发口径规则甲板(图1).这些Calibre引擎在被编辑的形状附近执行快速、递增的检查,导致几乎即时反馈设计规则违反和推荐的规则遵从性。P&R工具中的这种即时反馈使P&R工程师能够实现目标、按需放行DRC,并验证修复,而不需要进行完整的批量DRC迭代。而且,由于Calibre验证是透明实现的,因此几乎没有学习曲线。

Calibre RealTime Digital接口消除了P&R工具内置设计规则与合格的Calibre规则组之间的任何差距。因为Calibre RealTime Digital可以执行所有检查能够与Calibre nmDRC平台一起运行,包括推荐规则、模式匹配、基于方程的DRC、首选金属方向规则和多模式,P&R工程师现在可以快速发现和解决复杂的错误,并实现布局优化,例如:

- 多模式错误

- 高密度区域的间距误差

- 通过互换

- 功能/定时信号短裤

- 界面错误

- 信号电迁移(EM)错误

- Re-tapeout检查

尽管在P&R工具中执行这些检查和优化的能力为设计和验证流程提供了显著和即时的改进,但在P&R流程中,按需放行质量DRC还有其他好处。

对于DRC错误,通常有多个修复选项可用。由于传统批量DRC流程的时间限制,工程师通常采用最简单或最明显的解决方案,即使该解决方案对于实现设计的功率、性能和面积(PPA)目标不是最理想的。

有了立即结束质量的DRC反馈,工程师可以快速执行“假设”分析,运行多个修复程序来确定最佳解决的设计。对于DFM推荐的规则,他们可以在每次优化后重新检查DFM分数,以确定是否接近或已经达到目标DFM分数。

每个新的流程节点都会带来新的和修改过的设计规则。设计师可以简单地使用Calibre RealTime Digital界面在布局上运行规则,并立即看到其影响,而不是忍受通常乏味的审查和解释这些规则。通过亲身体验这些效果,工程师可以很快地看到理解规则的参数和应用.在当今快速变化的市场中,让您的设计尽可能快地通过生产可以提供一个显著的竞争优势。

通过在P&R环境中访问按需关闭质量的DRC,设计团队现在能够加快DRC的关闭,节省了tapeout时间表中的数周时间,同时最大限度地减少人力和计算资源的使用。与此同时,正确的施工方法为设计公司提供了信心,他们的高性能设计充分优化了PPA和制造。成功之路变得更平坦了。

作者