为了说明在buck变换器的效率中起作用的因素,下表列出了常用的公式估计最大的电力损失。利用这些方程可以快速地确定要使效率最小化的参数。降压变换器设计中的主要损耗取决于电路的具体工作条件,因此,为您的应用执行下面的计算是很重要的。你可以点击表格放大,以便查看。

效率参数

从这些方程中,可以利用下列参数来提高降压变换器的效率。请记住,通常输出电压和电流是由负载要求确定的。

参数最小化为高效率

开关频率(f西南)

降低开关频率将降低mosfet、整流器和电感铁芯的损耗。实际考虑通常限制开关频率。随着开关频率的降低,电感和电容必须增加,才能达到

保持一个可接受的电感电流纹波和输出电压纹波。因此,电感器和电容的物理尺寸会增加,在某些应用中可能不被接受。

在低开关频率下,导通损耗将占主导地位,进一步降低开关频率几乎得不到什么。在大多数负载点应用中,可接受的低频范围约为150至350 kHz。

开关频率远远大于350千赫是可能的,而保持良好的效率,只要在选择mosfet谨慎。今天的mosfet允许在开关频率达到1.5兆赫兹的合理效率,而没有实质性的成本惩罚。

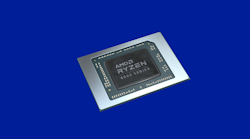

高端MOSFET

在高侧MOSFET中,导通损耗和开关损耗都是重要的。传导损耗与R成正比DS(上),而开关损耗与栅电荷Q成正比G, MOSFET的。不幸的是,对于给定的MOSFET制造过程,低RDS(上)设备将趋向于有一个较高的门电荷,反之亦然。决定哪个MOSFET参数是最好的优化取决于占空比和开关频率。对于低占空比(< 0.5),开关损耗往往占主导地位,特别是在高频率。在这种情况下,重要的是使栅电荷最小化。对于高占空比的情况,导通损耗起着较大的作用,因此减小R是很重要的DS(上).

下部MOSFET

与高侧MOSFET不同,低侧MOSFET的漏极到源极的电压在开启和关断过渡期间要低得多,这是由于其体二极管在死区时间的传导。因此,低侧的开关损耗通常可以忽略不计。这是幸运的,因为低侧开关损耗的计算要复杂得多(见参考文献2)。选择具有最低可达到R的低侧MOSFET是最有益的DS(上).低的RDS(上)mosfet需要更大的模具面积,因此,可以预期在一个更大的集成电路封装,相对更昂贵。

为了确保体二极管的贡献是最小的,一个低正向电压肖特基二极管应该放置在外部跨越QLS或选择集成MOSFET +肖特基器件。

功率二极管

二极管的功率损失主要由正向电压V决定F.肖特基二极管应该在任何可能的情况下使用,因为它具有非常低的正向电压(~ 0.3V)和最小的反向恢复时间。

同步与非同步的

在大多数应用中,特别是那些工作在低占空比和接近满载电流的应用中,同步降压比非同步降压更有效。当负载较轻或占空比很高时,非同步buck有时可以提供更高的效率。更多细节请参见参考资料3。

电感器

电感的功率损耗主要是由绕组的直流电阻、DCR和磁芯材料内的磁滞引起的。为了减少直流导通损失为一个给定的电感,线圈应使用更大直径的电线。为了减少铁芯损耗,应选择较低的开关频率。这两种方法都将导致物理上更大的电感,可能更昂贵,但将实现更好的效率。关于电感器功率损耗的更多细节请参见参考资料1。

为了识别低DCR等级的电感,需要寻找电流规格高于降压设计要求的电感。

其他损失

如果使用适当的设计实践,到目前为止所描述的方法可以提供很大的效率收益。在实际的开关降压变换器电路中有许多额外的损耗,也可以通过一些详细的分析来降低这些损耗。减少这些可能只会带来很少的回报;但是,如果操作条件不典型或为了达到最大的效率,则应考虑它们。

Buck变换器的额外功率损耗

●充电HS MOSFET的输出电容

●充电外部肖特基二极管的电容

●阀体二极管反向恢复损耗

●输入输出电容ESR损耗

参考文献

1.伊奇霍恩说,特拉维斯。“在电源设计中容易估计电感损耗”,电力电子技术,2005年4月。

2.在下赛季,乔恩。“基于Excel模型的AN-6005同步Buck MOSFET损耗计算”,飞兆半导体,2006年1月。

3.诺瓦科夫斯基,里奇和唐宁。“同步与非同步Buck变换器的效率”,TI模拟应用杂志,2009年第4期。

4.应用笔记4266,“开关模式DC-DC变换器电源的效率入门”,Maxim Integrated Products, 2008年12月。