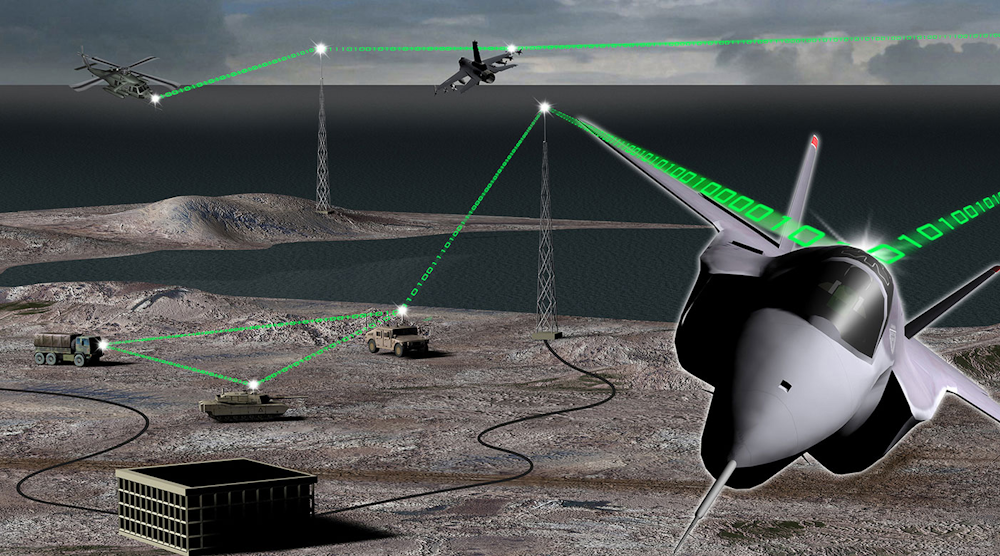

对于军事情报,监视和侦察(ISR)应用,如雷达,EO / IR(电光/红外线)或宽带埃林特(电子智能),持续的问题是如何最好地处理扩大的“Firehose”通过越来越多的宽带宽平台传感器提供的数据。为了处理这种大规模的数据流入,并且处理它所需的复杂算法,最先进的计算引擎和数据传输机制是必不可少的。

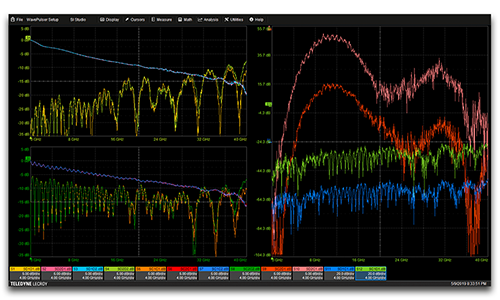

部署的高性能嵌入式计算机(HPEC)系统旨在支持这些应用程序通常具有高性能FPGA,GPU和数字信号处理器的异构架构,或DSP(常常英特尔基于Xeon-D的模块)。GPU为复杂的数学算法提供了大量调整的浮点核心,这使得它们是处理ISR应用中使用的复杂算法的理想选择。相比之下,单个英特尔Xeon-D处理器可以提供〜600 MFLOPS的峰值吞吐量,而NVIDIA的Pascal P5000 GPU支持6.4 TFLOPS的最高性能。

更严格的集成

今天,ISR系统集成商有三个主要目标:最小化延迟,最大化系统带宽,以及在给定的SWaP约束下优化配置灵活性。为了解决这些问题,OpenVPX模块的主要COTS供应商正在寻找方法来提供计算元素之间更紧密的集成。

一开始,FPGA预处理的传感器数据需要复制到CPU上,CPU再复制到GPU上进行进一步处理。然后,NVIDA引入了GPUDirect,它增加了将数据直接从FPGA或网络接口(如Mellanox Infiniband)移动到GPU的能力。通过消除额外的副本,延迟和背板利用率都降低了。

这种方法可以很好地工作,直到进入的数据量使系统不堪重负,例如,在下一批数据到达之前,其中一批数据还没有完成处理。这可能是由于传输系统过载(I/O限制)或GPU没有在要求的时间帧内完成计算(计算限制)。

当使用GPU时,限制因子通常是I / O,并且通常通过采用传入数据的循环分布和/或流水处理处理阶段来解决这一点。不幸的是,随着传感器数据继续增加,显而易见的是,需要新技术。

PCI Express

在OpenVPX系统中,fpga、gpu和cpu之间的标准接口是PCI Express (PCIe),它提供了进入和离开处理器的最快路径,并根据定义,通过扩展平面连接到其他设备。通过PCIe连接卸载以太网可以减少延迟并增加吞吐量。

基于最初的PCI并行总线设计,PCIe由一个称为根复合体的“主”主机控制,该主机扫描总线以查找和枚举所有连接的设备。当一个PCIe交换机将多个设备连接到一个根节点上时,称为TB (transparent bridge),所有设备都在一个地址空间内运行。对于TB,不能连接两个根节点(处理器),因为会出现内存地址冲突。

当PCIe交换机端口配置为非透明网桥(NTB)时,根节点不会查看枚举该交换机端口以外的设备。因此,当两个处理器中的任何一个枚举其NTB端口时,端口请求该处理器上的内存。NTB端口为任意一端提供公共内存地址转换。

多播

减少延迟的下一步是将传入数据多播到多个gpu。直到最近,在部署的ISR系统中多播gpu还不现实,因为之前的PCIe实现受到了传统的一对一连接设计限制的阻碍。如何使用PCIe链路跨多个gpu组播数据的问题,增加了已经很复杂的PCIe接口编程和建立桥和根复合体的任务。

包括在Curtiss-Wright'sOpenHPEC Accelerator Suite,Dolphin互连解决方案'PCI Express(PCIe)Fabric通信库提供了从PCIe接口挤出每一盎司性能所需的软件。它还通过向简单的API摘要将诸如耗时的代码抽象出来,简化PCIe编程。

软件基础设施共享内存集群互连(SISCI)是一种成熟的API,是交换数据的最快方式。pci - ntb可用于PIO (programming IO),用指针直接访问远端内存,延迟最低;也可用于RDMA (remote direct memory access), PCIe-NTB的DMA控制器将数据从远端内存复制到本地内存,带宽最高。

SISCI减少延迟的特性之一是反射内存/多播。PCIe交换机将同时发送所有连接端口的数据,这意味着所有节点在连接到单个交换机时几乎同时接收数据。当使用多个网桥时,每个交换跳将在数据延迟上增加一个微小的延迟。

在典型的基于背板的ISR系统中,CPU直接绑定到位于其XMC mezz卡或机箱中单独插槽的GPU上。例如,6U OpenVPX板上的双xeon - d通过PCIe交换机连接。同样,一个6U的GPU卡可能有两个GPU通过PCIe交换机连接到另一个和背板上。使用这种双板6U DSP和GPU系统“切片”,一个Xeon-D可以控制两个GPU,或者每个Xeon-D可以控制一个GPU。由一块DSP板和两块GPU板组成的三块板组合,一块Xeon-D控制上行GPU卡,另一块Xeon-D控制下行GPU卡。

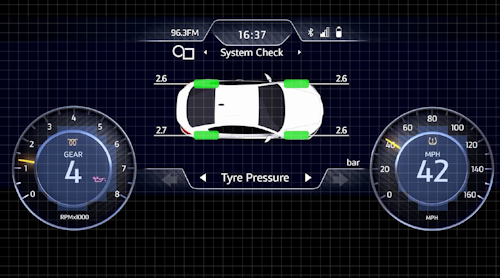

这是一个3U配置的示例。

如果系统是基于较小的3U OpenVPX形式因素(见图),延迟问题变得更加敏锐,因为CPU板可能只有一个X4 PCIe链接。如果3U系统不包括中央开关,则该解决方案变得越来越慢。

在组合系统中创造灵活性

ISR系统可以运行多种模式,但现在系统集成商也希望能够将雷达和电子战等系统合并到一个单独的处理盒中。在这样的配置中,每个系统的模式之间的数据流和计算需求会有很大的不同。由于gpu和fpga是用电缆连接的,或通过背板连接的,灵活性可能是棘手的。可以通过重新配置PCIe桥接端口来实现一些灵活性,但是如果CPU可以借用PCIe总线上的GPU、FPGA甚至非易失性内存呢?

使用Dolphin的PCIe设备借贷,可以在没有任何软件开销的情况下通过PCIe网络借用设备。设备贷款是重新配置系统的简单方法和重新分配资源。借贷功能使网络上可用的设备用于临时访问。借用功能搜索可用的设备,然后可以根据需要暂时借用所选设备。工作完成后,将释放设备。

在GTC 2019年会议上,Dolphin展示了其概念证明软件库,该软件库用于使用GPU Direct创建面向GPU的应用程序,使用GPU和商用NVMe磁盘。PCIe ntb的内存映射功能用于在连接到不同根节点的gpu和磁盘之间建立高效的I/O数据路径,允许多个gpu访问远程磁盘。

虽然gpu对于各种高性能ISR应用程序具有明显的优势,但一些设计师担心这些设备所表现出的确定性不足。好消息是,英伟达正在努力改善其gpu的确定性。在CUDA中,NVIDIA将公开api来描述任务以及任务之间的依赖关系,从而提供对它们的更多控制。在系统层面,NVIDIA正在开发一种定时触发调度器。

遗留代码呢?

虽然新系统可以很容易地从GPU架构的这些最新进展中受益,但当然,还有许多遗留软件仍在使用中。OpenACC有助于保护这些遗留代码中的大量投资。这是一种标准的编程语言,它使优化和移植旧的现有串行代码到多核处理器,如Xeon-D或GPU,一个非常简单的过程。

OpenACC需要的只是一个HashTag和代码运行的平台的定义。反过来,代码将能够在目标板上运行。这使得可以具有优化晶片,其使得代码能够在小增量阶段(例如一个时间)并行化,基本上允许系统在优化/移植现有代码时采用“婴儿步骤”。虽然在CUDA中的手写代码上没有效率,但结果令人印象深刻,而且在几周内,可以为GPU优化和移植历史悠久的遗产代码来提供很大的结果。

在异构系统中寻找可能的最佳信号处理性能时,最好考虑使用GPUDirect来减少“中间人”CPU,以减少延迟。下一步是探索从前端到多个gpu和cpu的多播,即使数据必须通过几个桥接。

为了获得最大系统灵活性,集成商应查看可以使用PCIe设备借贷借用的设备的库系统。使用SISCI API按时和预算保持软件,而不是从头开始写入所有PCIe代码。对于遗留的快速转向搬运,在OpenACC中与Pragmas一起玩。这些策略对于寻求提高性能,延迟和灵活性的任何ISR系统集成商都可以有用的指南。

Tammy Carter是高级产品经理,GPGPU和Software,Openhpec,ATCurtiss-Wright防御解决方案。