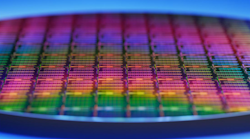

通过将硬核RISC-V CPU与最新的FPGA集成微膜, aMicrochipcompany, has further bolstered its RISC-V support. This is the same approach that Intel/Altera and Xilinx have done with Arm cores and their system-on-chip (SoC) FPGA offerings. Microsemi also has an FPGA with a hard-core ARM Cortex-M3, but itsMi-V initiativehas been pushing soft-core RISC-V support in its FPGA lines.

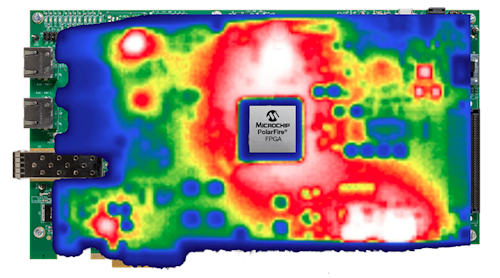

Microsemi的64位RISC-V SOC FPGA基于其Polarfire FPGA。该方法具有许多优势,包括简化的设计,更容易保护。该设计不受光谱和熔融风格的攻击。该公司还包括反篡改支持,差异功率分析(DPA)抗性比特斯流编程,密码学结合的供应链保证,身体上无谬的功能(PUF)支持,侧向通道的抗沟通式加密处理器和真实的随机数字发电机。此外,所有内存都具有单纠正,双纠错检测(secded)支持。

The RISC-V approach also provides a lower-cost migration path to an ASIC for those designs that are more geared to high volumes. The kicker is that these cores can be configured to provide deterministic operation.

1. Microsemi’s PolarFire SoC sports five cores, including an E51 and four U54 RISC-V cores connected to a common L2 cache.

The PolarFire SoC consists of a flash-based PolarFire FPGA and five 64-bit RISC-V cores(Fig. 1). One is asifiveE51 RV64IMAC core and the other four are SiFive U54 RV64GCs. SiFive has been delivering a number of different RISC-V cores to chip designers.

连贯的开关将核心连接到DDR4/LPDDR4存储器控制器和连接到Polarfire FPGA的AMBA开关。除了安全启动支持外,还有128 KB的芯片闪存闪存。

The E51 is designed as a control monitor with physical memory protection (PMP) unit while the U54 cores add a memory management unit (MMU) suitable for running operating systems like Linux. The cores have an in-order, five-stage pipeline. Each core can have features turned off, such as the branch predictor providing a deterministic execution environment. The 2-MB L2 cache can also be customized so that portions are locked down in scratchpad mode, enabling support for coherent message buffers(Fig. 2). These can be accessed by any core even if it’s not running in deterministic mode.

2.可以将RISC-V内核配置为确定性操作,并且可以将L2缓存分配到直接访问存储器中。

以这种方式配置任何核心的能力为开发人员提供了更大的灵活性。可以使用各种组合,例如Linux在所有四个U54内核上运行时以确定性模式运行的E51。另外,一个U54内核和E51内核可以在确定性模式下使用其他运行Linux的U54内核进行操作。所有人都可以共享连贯的内存子系统的所有分区。

The I/O space also supports hardware partitioning. This allows the crypto hardware to be isolated with the E51 or maybe even one of the U54 cores.

The chips provide a robust debug environment. The FPGA has the SmartDebug dual-channel logic analyzer built in. The RISC-V cores have an instruction trace, 50 hardware breakpoints, debug locks, and a fabric logic monitor. There’s also an AXI bus monitor.

微膜is providing developers with complete access to the security features of the chip, including the secure-boot source code. This gives advanced developers the ability to check or replace this code to customize the secure-boot process.

PolarFire SoC不会immediatel可用y, but developers can take advantage of the free Renode virtual development emulator model created byAntmicro. The emulator model supports debugging the entire processor subsystem.

Microsemi的Polarfire RISC-V平台提供安全,实时,确定性,不对称多处理(AMP)支持。除了RISC-V内核外,它具有令人印象深刻的安全性和调试功能。将提供延长的温度版本。低功率,基于Flash的FPGA以及低功率RISC-V芯提供了一个低功率的解决方案,其他平台可能会发现很难击败。

微膜will be one to watch in 2019 when the chips are released.