RISC-V是一种用于开发开源处理器的RISC指令集标准(看 ”RISC-V(五)活着!“)除了专有实施。它也是主要的软核处理器架构MicrosemiFPGA。MicroSemi也提供了硬核FPGA,支持其他软核架构,如ARM的Cortex-M1。

开发和使用MicroSemi的软核心处理器通常包括Libero SoC FPGA设计工具和基于Eclipse的软件版集成开发环境(IDE),除了FPGA平台(图。1)。

1. RISC-V Microsemi FPGA的开发流程以Libero开头的硬件设计和软件设计的软件设计。

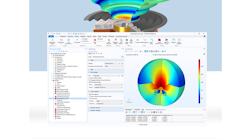

SoftConsole 5.1是最新的化身,它还支持RISC-V平台的范围。开发人员可以使用SoftConsole插件选择RISC-V配置(图2)。例如,除了单个,双浮点支持之外,该体系结构还支持32个,64和128位寄存器设置。SoftConsole目标是此时可用的32和64位平台。压缩指令集被添加到具有更有限的直接寄存器访问的混音中的16位指令格式,但它可以降低代码大小。

Libero和SoftConsole通过配置文件链接,使得Libero FPGA设计包括一个外围设备和核心集合,可以为IDE提供细节。反过来,编译器将能够支持硬件。

MicroSemi在易于安装的软件包中提供其软件,以最大限度地减少任何集成家务。SoftConsole 5.1支持Windows和Linux主机,包括Windows 7和10,CentOS,Red Hat Linux,Ubuntu和OpenSuse。这些包括Standalone安装程序,简化安装。SoftConsole 5.1基于Eclipse Luna 4.4 SR2和CDT 8.6.0 for C和C ++支持。对目标操作系统的支持最终将包括Freertos,Safertos,Liteos和MicriumμC/ OI和III。

2. SoftConsole的RISC-V Eclipse插件允许开发人员选择目标配置功能,以便编译器生成相应的代码。

SoftConsole还附带一个固件目录,用于软件外围设备,如PWMS和串口,可用于FPGA。这些司机是MISRA和BlackBerry QNX Neverlino标准的。MISRA C是Automotive环境中的编码标准最初定位安全性,但也已用于嵌入式应用程序(看 ”Misra C:2012:改变的充足理由“)。

调试器支持MicroSemi的SmartDebug以及Openocd。Openocd允许该工具集除了MicroSemi FPGA目标之外还可以与其他RISC-V平台一起使用。SoftConsole将使用MicroSemi的北极极,RTG4和IGLOO2 FPGA。它也支持Sifive基于第一个RISC-V微控制器的HIFIVE1(看 ”第一个开源RISC-V芯片到达“)。

RISC-V领域的竞争对手有很多优势。例如,与ARM Cortex-M1相比,其开源性质意味着RTL可用于查看,与ARM Cortex-M1使用加密RTL。无论在设计中使用多少个核心,MicroSemi RISC-V实现都没有许可费用。同样地,迁移到ASIC的设计也是免版税的。