你将学习:

- 为什么PCB工作流程需要不同层次的EDA功能。

- 如何为不同的PCB任务使用合适数量的EDA。

- 哪种PCB场景需要最大EDA和最小EDA。

设计PCB是一项复杂的工作,但没有这样的事情一个这是处理工作的最佳方式。有时候,工程师想要采取一种“快速而肮脏”的方法,只是从他们的头脑中获得一个想法,看看它是否可行。其他时候,他们想要“清除杂草”,并使用他们所使用的所有电子设计自动化(EDA)工具。

为了能够按照他们喜欢的方式来处理PCB设计工作流程,避免被硬塞进预定的工作方式,工程师需要使用从“最小EDA”到“最大EDA”的全功能。这有点像金发姑娘的情况:确保EDA不是太多,也不是太少,而是根据手头的任务来确定合适的数量。

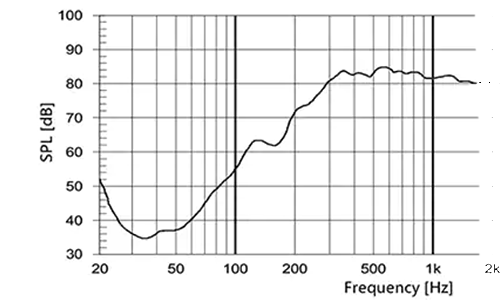

考虑以下三个场景,它们说明了工程师在创建PCB的过程中可能面临的不同任务(见图)以及如何最有效地解决这些问题。

任务#1:快速、轻松地测试布局

有时,工程师想要跳过原理图过程,从头开始构建他们的原型作为一个板设计。他们知道自己想要什么——就在他们的脑海里。我们的目标只是简单地列出一些东西,看看它是否有效,而不是通过整个传统的原理图过程。如果-在测试布局后-它工作,然后他们可以把它交给一个团队成员生成一个原理图。

这种能力大大减少了喜欢这种方式的工程师的设计时间,因为他们知道自己脑子里想的是什么,可能不想做任何更详细的事情,而只是在一张餐巾纸上划掉它。有句老话说得好:有时候少即是多。额外的功能只会限制他们在这个特定任务中的风格。

任务#2:导出绑定线或创建贴花

在某些情况下,工程师不需要完全了解EDA,但他们确实需要能够“尝试”一些EDA领域的知识。在这些场景中,将更高级的功能放在一边是有帮助的,工程师可以根据他们的工作流首选项轻松地使用这些功能。

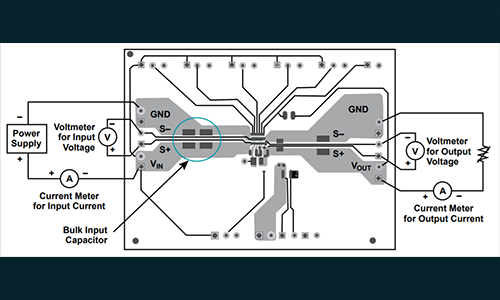

例如,通过访问独立的键合线导出解决方案,设计师可以从一个简单的DWG文件开始,该文件包含线条、弧线、折线和其他设计元素,表示从芯片到衬底的键合线。然后,他们可以使用绑定线导出器来“智能化”DWG,并将文件输出到绑定线机器。这对于只想创建芯片设计的图形表示的设计人员来说是非常理想的。

同样,有些人可能不使用EDA,但仍然需要为Gerber、贴花和其他设计元素的GDS翻译。当这个功能被分解成一个独立的选项时,它可以支持这些小众工作流,而不会给工程师提供超出他们需要的功能。

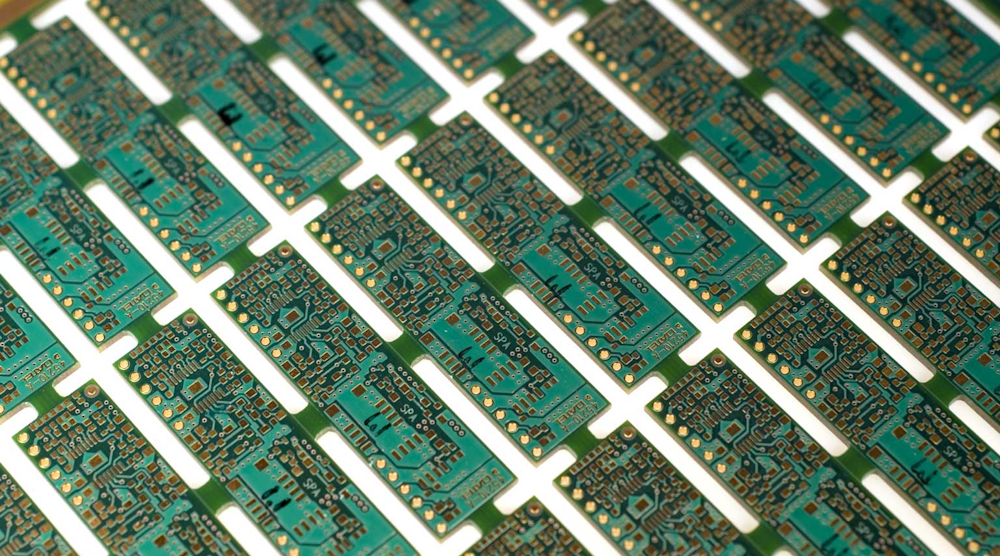

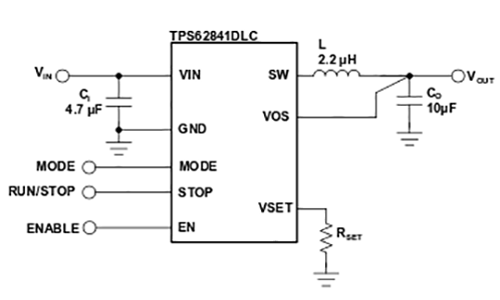

任务#3:使用厚膜

有些任务需要全EDA,厚膜陶瓷设计就是其中之一。除了键合线数据导出外,它还需要一些工具,如增强的动态掩码生成器、面板生成和odb++输出,以支持键合线机器。

这些工具——除了用于批量或分段去除腔体材料的咬入数据,以及用于正确输出到生产的格伯、孔和冲孔数据的控制——都有利于低高温共烧陶瓷设计。

在厚膜上工作的能力是特别有益的,因为越来越多的制造商正在转向它。制造厚膜比继续支持低高温共烧陶瓷设计等工艺要便宜得多。你可以从一个方面数出仍在生产LTCC和HTCC材料的大公司的数量。

因此,拥有有效地处理厚膜的工具,不仅仅是以一种首选的方式完成工作的问题。关键是要与时俱进,适应行业内不断变化的宏观趋势。

每一个人

上述场景清楚地表明,在PCB设计中不存在“一刀切”的东西。有时候,“轻触”是最有效地处理任务所需要的;其他时候,它需要“工业实力”的EDA能力。

对于他们来说,软件供应商需要确保他们有一个足够强大的基础,能够为工程师提供适合他们的工作流程的工具,跨越任何这些场景,交付适量的EDA功能。

一旦他们手中有了这些工具,工程师就可以以对他们最有意义的方式处理PCB设计的各个方面。因为虽然最终产品可能非常相似,但设计它们的方法应该是任何东西但那

_and_Applications.png?auto=format&fit=crop&h=139&w=250&q=60)