用户的Xilinx7系列FPGA将在两个开发工具之间进行选择。现在在第13次修订版中,Xilinx的ISE支持所有公司的FPGA。Vivado Design Suite支持所有系列7 FPGA,并将成为来自Xilinx的所有未来FPGA的开发工具。公司确实有一个向上迁移路径,Vivado能够加载ISE项目。现有项目可能会留在ISE上,但新项目可能会利用Vivado及其改进的能力。

图1所示。1.2M逻辑单元Virtex-7 2000T FPGA上的布局具有挑战性。左侧使用ISE完成,需要13个小时和16g字节的内存,而右侧使用Vivado完成,运行5个小时,只使用9g字节。

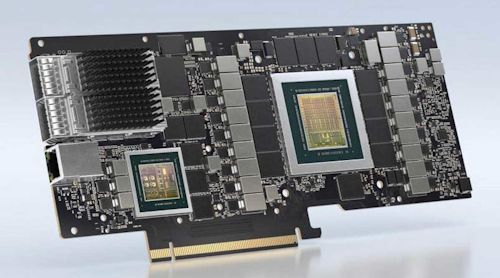

Xilinx的多片1.2M逻辑单元Virtex-7 2000T FPGA(看“FPGA切片之间的10,000个连接”在electronicdesign.com上)突出了Vivado的优势之一及其改进的地方和路线技术(图。1).更快的工具使用更少的内存来计算最佳布局,通过使用解析求解器找到全局最小值,而不是像ISE那样搜索局部最小值或像大多数其他系统那样执行地点和路径(图2).

图2。Vivado的place-and-route为FPGA布局找到全局最小值。

Vivado解决了N个方程,M个未知数加上成本函数,可以解决时机,电线长度和拥塞。确定性的地方和路线还提供自动时钟门控支持。通常,功率降低30%,逻辑增加1%。可以通过组件知识属性(IP)或设计层次结构中来管理此优化支持。

Xilinx可能已经留下了ISE,如果只是改善地点和路线编译器的问题。但是,Vivado在设计师接近FPGA设计问题和实施设计方面的方式纳入了重大变化。这就是为什么Vivado从头开始设计,重点是IP集成。它利用了分层芯片规划和设计方法,并支持多域和多模(如Virtex-7 2000t)物理优化。设计层次结构会影响到电源管理的地方和路线的所有内容。

IP Integration使用带有设计人员从目录中选择项目的拖放接口。旨在提供的物品AMBA ax4(高级可扩展接口4)支持可以通过拖动-链接操作自动连接。ARM开发了AMBA的ax4互连协议,并支持多种ARM硬核和软核处理器。Xilinx的Zynq-7000 EPP(可扩展处理平台)集成了支持AXI4的双ARM Cortex-A9内核,这一点也不奇怪(参见“FPGA包在双皮质-A9微“在ElectronicDesign.com上).

ISE提供了对AXI4的支持,但Vivado显著地扩展了这些特性。这个想法是通过构建来实现一个正确的设计。这并不能消除对详细逻辑设计的需求,因为该工具也可以用于此目的。同样,Vivado包含一个打包工具,可以创建项目并将其添加到目录中。

大型系统可以从组件快速构建,但它们需要更长时间才能编译。增量编译可能会显着减少此时间。Vivado的增量性质解决了工程变更订单(ECO)以及涟漪变化作为项目的设计变化的影响。它包含自己的生态数据库。

组件可以是可配置的,设计人员可以在不改变底层系统的情况下尝试各种约束。设计师然后可以快速检查替代方案,尤其是增量汇编。此外,Vivado的模拟支持比ISE快三倍。它支持硬件共同仿真,也可以提高仿真时间100倍。

Vivado综合开发环境(IDE)是基于Jide(图3).它还包含了工具命令语言(TCL)用于高级脚本。TCL通常用于嵌入式应用,用于快速原型设计。Xilinx的软件开发套件(SDK)仍然基于Eclipse IDE,并使用使用Vivado创建的硬核和软核设计。

图3. Vivado的IDE基于Jide。

该工具有三个版本。免费的webpack包括SDK软件。它具有有限的模拟支持。设计版具有完整的仿真和调试包,包括逻辑分析仪和高速串行I / O分析。高端系统版增加了高级合成和DSP生成。

Vivado是Xilinx的一个重大变化,它向竞争对手发起了挑战。它为传统的FPGA开发人员提供了足够的增强,但增量的分层设计方法和AXI4联动为许多其他用户打开了大门。ISE将继续使用,因此不会立即强制迁移,但这是Xilinx及其客户的未来趋势。