自适应计算加速平台(ACAP)赛灵思公司,已经正式发布,现在它被称为Versal(图1).它极大地扩展了Xilinx的Zynq Ultrascale+ MPSoC,该系统拥有多个硬核Arm处理器以及互补的硬核外围设备。

然而,Versal的一些功能使其与Zynq Ultrascale+有很大的不同。首先,Arm Cortex-A72s和实时Cortex-R5s等处理核心与平台管理控制器(PMC)绑定。其次,该处理综合体功能齐全,可以启动并使用PMC对芯片的其余部分进行配置。这与早期Xilinx平台的情况不同。它可以极大地简化开发和部署,因为软件可以控制系统并在已知的配置上运行。

1.Versal是Xilinx的自适应计算加速平台(ACAP)的实现。

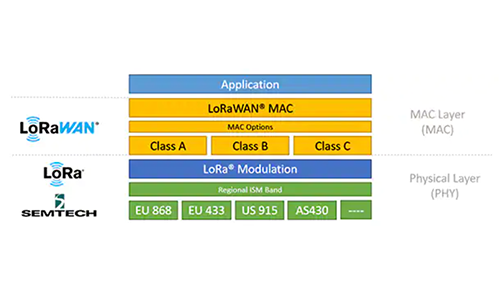

可适应硬件(AH)组件本质上是我们已经了解并喜爱的FPGA,但它已经在更大的计算环境中得到了增强和优化。它仍然提供了一个完整的配置结构,并且迁移相对简单,尽管存在差异。一个主要的区别是把所有东西都联系在一起的芯片上网络(NoC)。

NoC将AXI挂钩到AH中(我仍然认为我们需要将其称为FPGA),但也将其连接到芯片上的其他所有内容,包括AI和DSP引擎。DSP支持的移动可能是从现有fpga迁移到通用的最困难的方面。NoC为所有设备提供一致的接口。此外,Xilinx对AXI接口进行了标准化;因此,即使是现有fpga上的软设备看起来也和Versal中的任何硬设备或软设备一样。

AH的其他一些变化是可定制的内存层次结构和比现有平台快8倍的动态重新配置。这是AH重用的关键,也是使重新配置系统更可取的关键。缓慢或困难的重新配置通常会消除它作为特定应用程序的选项。

2.Versal家族有6个版本,AI Core和Prime是最先推出的两个版本。

Versal家族目前包括六个配置,其中两个已经列举到目前为止(图2).这两个是Versal AI core和Versal Prime。

AI Core和Prime

通用AI Core是包含AI加速功能的中程人工智能平台。Versal Prime系列没有人工智能加速功能(图3).AI组的其他系列将增加AI组件,例如为AI RF系列增加高速模拟支持。这与Zynq UltraScale+ RFSoC类似,具有多gigasample/s模数转换器和数模转换器(adc和dac)。Prime、Premium和HBM(高带宽内存)版本没有或有限的硬件加速AI支持,但添加了在高性能计算(HPC)平台中常见的HBM等功能。

3.《universal Prime》(左)放弃了AI Core(右)中包含的AI加速功能。

AI Core中的AI引擎是具有自己内存的1ghz VLIW/SIMD矢量处理核心(图4).这些连接在一个数组中,不要与NoC混淆。紧密耦合的存储器可以组织在不同的存储器层次结构中。硬件和软件都是可编程的,以支持当前和新兴的人工智能深度神经网络(DNN)模型。

4.Xilinx的AI加速器由一组具有紧密耦合存储器的向量处理核心组成。

Versal还包括一系列与NoC绑定的硬件,如主机接口,如x16 PCI Express Gen 4、axis - dma和CCIX(见6)。Xilinx是CCIX财团用于管理高速缓存相干互连(CCIX)规范。CCIX是一种高速互连。

内存接口包括DDR4-3200、LPDDR4-4266、HBM。网络接口包括100G多速率以太网、600G以太网和Interlaken,以及支持AES、IPSEC和MACSEC的600G加密引擎。支持32G、58G PAM4、112G PAM4的高速SERDES芯片也将上市。

RF信号链是用于RF Versal的化身。支持包括多gigasample/s dac和adc以及集成的数字下变频/数字上变频(DDCs/DUCs)。软件决策前向纠错(SD-FEC)也是其中的一部分,它对5G等高速通信系统至关重要。

最后,MIPI D-PHY支持高达3gb /s的传感器。直接支持NAND和其他存储器。LVDS和gpio外围补全。

这个框图没有显示加密加速以外的安全特性,但是还有更多的特性没有在图中列举出来。这些处理器支持Arm的TrustZone,这是信任的基础,因为软件是最先出现的。NoC可以被分区,这样特定的处理器或AH块就会被限制在可用的设备和服务上。这种支持对于像汽车或航空电子设备这样的分区系统非常重要,在这些系统中,只有底层系统配置能够得到保证和隔离,才有可能获得认证。NoC还实现了实时嵌入式系统所需的一些特性,如支持质量(QoS)。

由于NoC和标准的硬件组件,开发更复杂,但可能更容易(图5).Vivado的统一软件开发环境将解决硬件加速器,包括AI和DSP引擎。值得注意的一件有趣的事情是,Xilinx的主要语言列表中有Python,它还指定了C和c++。Python是人工智能工作中使用的主要语言之一。此外,开发环境考虑在AH中实现的加速器。这应该使第三方逻辑实现的支持更容易管理和合并到应用程序中。

5.Xilinx将提供一个统一的开发环境来为Versal开发应用程序。

通用芯片的规格与Zynq非常相似。VM1102通用Prime是该系列的低端产品,包括472个DSP引擎、352个系统逻辑单元、超过150K的查找表(LUTs)和256kb的片上ECC内存。Versal Prime系列有一对cortex - a72和一对Cortex-R5s,双以太网端口,USB-2.0和双CAN-FD。它不包含CCIX支持,但有一个x8 PCIe Gen 4端口。它可以装入21 × 21毫米的芯片中。

高端的通用Prime VM2902拥有超过3000个DSP引擎、2154个系统逻辑单元和近100万个lut。其中包括6个内存控制器,一个支持CCIX的x16 PCIe Gen 4端口,以及一对x8 PCIe Gen 4端口。

AI系列从VC1352开始,VC1352拥有128个AI引擎和928个DSP引擎。高端VC1902包含400台AI发动机和1968台DSP发动机。它们具有与通用Prime类似的计算、I/O和内存补充,尽管AI平台有更多的以太网MAC支持,VC1352有SD-FEC支持。

ACAP

Xilinx的ACAP架构改变了fpga和asic之间的动态关系。FPGA结构仍然是Versal生态系统的一部分,但它被一个更大的核心设备阵列所包围,这些设备将像ASIC一样高效地实现。同样地,大型soc将始终拥有NoC之类的东西来连接不断增长的设备补充。

ACAP方法有许多好处,包括由于采用了硬核而带来的功耗和性能效率。例如,Xilinx希望交付一个只使用5 W的Versal核心。拥有更多固定的功能也可以简化软件,因为有更多的标准目标可供操作。另一个关键因素是NoC,因为芯片上的通信比芯片外的通信效率高得多。这也减少了设备所需的引脚数量。最后,与FPGA相比,对于类似的功能,FPGA的成本应该更类似于asic,因为与硬逻辑相比,FPGA结构在占用空间和总体成本方面更昂贵。

通用器件显然将用于ASIC的长期目标的设计和开发目的。然而,与FPGA或更基本的FPGA soc相比,它们的成本更低,功耗需求更低,性能特征更高,因此更有可能在最终部署中应用。

Versal希望能在设计上找到最佳点,解决对性能和通信要求较高的广泛应用。目前还没有类似的解决方案,所以想要进入ACAP领域的供应商将在这一点上迎头赶上。Versal为开发人员提供了一个不需要ASIC或更复杂的模块或PCB上的芯片集合的成本效益高的解决方案。