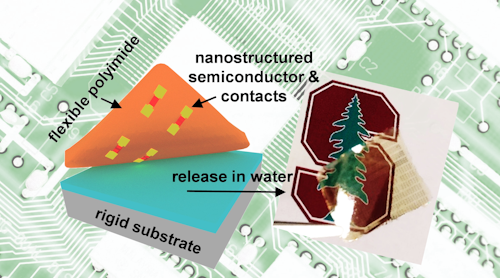

平面FD-SOI技术依赖于埋地氧化物(盒子)上的超薄硅层。超薄体晶体管内置在该顶部硅层中,它们提供了几种非常有吸引力的操作特性。可以使用两种类型的掩埋氧化物:标准145nm厚度,或10nm或25nm超薄(Utbox)。

从物理角度来看,非常薄的硅层使得位于晶体管主体下方的硅能够完全耗尽电荷。总结果是栅极可以精确地控制晶体管主体的全体积。这导致比散装CMOS晶体管更好的性能,尤其是当电源电压降低时。此外,FD-SOI不需要在通道中掺杂。

该技术的其他主要优点包括它解决了缩放,泄漏和可变性问题,以进一步收缩CMOS技术超过28nm。它提供了晶体管的非常好的静电控制,并将促进整体性能以及较低的功耗。

FD-SOI切断随机掺杂物波动,从而降低晶体管阈值变化。这使得能够在非常低的功率水平下实现稳定,密集和高屈服的SRAM功能。

最重要的是,FD-SOI将通过使半导体器件更容易地将半导体器件更容易地提高逻辑密度来帮助维护Moore的定律,这又增加了有助于保持法律滚动的逻辑密度。

此过程的可用性构建了允许大学和设计公司访问以前的CMOS几代的成功合作,包括45nm,65nm,90nm和130nm(后者在2003年被引入)。CMP的客户端还可以访问65nm和130nm的绝缘体(SOI),以及来自ST的130nm SiGe工艺。

共有170所大学和其他公司已收到ST的90nm CMOS过程的设计规则和设计套件。拥有200多个大学和公司已收到ST的65nm批量和SOI CMOS流程的设计规则和设计套件。

现在,ST的28nm CMOS批量技术正在由CMP提供,到目前为止大约60所大学和微电子公司已收到设计规则和设计套件。事实上,已经制造了16个集成电路。

CMP多项目晶圆服务允许组织获得少量的高级IC。28nm FD-SOI CMOS工艺的成本已固定为18,000欧元/ mm2,至少1mm2。