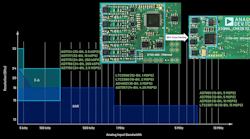

arm的新东西Cortex-R5(图1)和Cortex-R7(图2)准备发射40纳米。这两个架构扩展了几年前发布的实时Cortex-R4架构。这些高端多核处理器旨在处理从汽车到LTE的一系列应用。它们的实时性、安全性和高可靠性至关重要。

Cortex-R5是1.66 DMIPS / MHz双核架构。核心可以在锁定步骤模式下运行,需要冗余平台,例如汽车传动系和安全系统。它包括可选的节省空间单精度浮点单元(FPU)。它还将ECC用单位误差校正推动到内部总线和L1存储器上。

Cortex-R7核心以2.5 DMIPS / MHz运行,使其几乎是Cortex-R5的两倍。这Cortex-R7架构(图3)这是使用更深的管道和一些无序的执行。后者是有限的,保持实时编程。核心可以在SMP(对称多处理)和放大器(非对称多处理)模式下操作。Cortex-R7也有ECC全部支持。它可以解决更高的性能习惯,如LTE高级。

这两个架构都可以具有紧密耦合的存储器(TCMS),它直接与处理器寄存器集成。Cortex-R7还可以支持连接到数据和指令缓存的低延迟RAM。

Cortex-5的内部和外部I / O之间保持缓存一致性。Cortex-R7还维持通过AXI加速器一致性端口(ACP)连接的I / O设备的一致性。

Cortex-R7中断也可以针对处理器吞吐量或低延迟进行优化。这可以通过核心应用,允许一个核心提供最大吞吐量,而另一个处理中断。RemotoCessor中断路由提供核心之间的快速通信。