本文是一部分TechXchange:RISC V

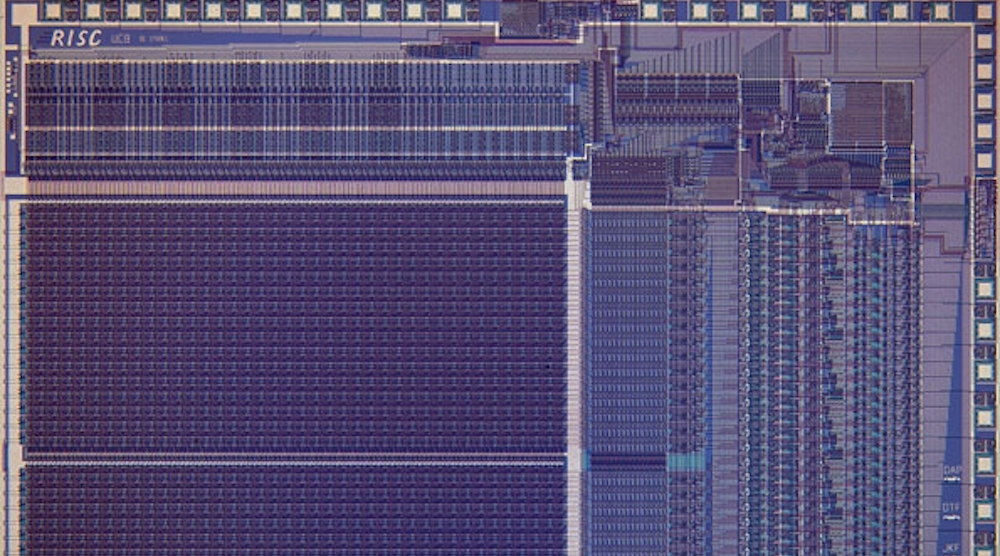

RISC-V(RISC 5)是一种紧凑、开源、指令集架构(ISA),是嵌入式应用的理想选择,包括物联网(IoT)的低功耗平台。它最初是在计算机科学部开发的伯克利加州大学的EECS部门(见图)它有自己的基础来促进它的使用和采用。

RISC-V于伯克利加州大学EECS部门的电脑科学部开发。这款模具射击是原始的RICV-I芯片。

RISC- v是一个真正的精简指令集计算(RISC)平台,使用显式的加载/存储架构。ISA使用32位指令,它没有条件代码,而是使用基于寄存器的比较分支指令。它基于一个包含32个寄存器的寄存器文件,尽管寄存器0包含一个值为0。系统可以配置16位、32位、64位和128位寄存器。没有硬件堆栈。跳转和链接(JAL)指令将程序计数器复制到寄存器。软件栈通常在需要时实现。其优点是可以实现不同的堆栈实现。

RISC-V实现的命名包括许多用字母表示的指令扩展。

- 我整型配置

- e嵌入式版本,只有16个注册文件

- 原子,实时指导

- 用于嵌入式应用的C-compact 16位指令集

- m整数乘法和除法

- f单精度浮点数

- d双精度浮点数

- q四精度浮点数

- G-general,包括IAFDP

对于SIMD支持等特性,还有其他扩展。一个典型的嵌入式实例化将被指定为RV32EC (RISC-V, 32位,16寄存器文件,紧凑指令集)。RISC-V的高端实现可以运行Linux等操作系统。

RISC-V是嵌入式应用的理想选择。基本系统的指令小于50个。即使包括浮点等特征,这使得能够添加其他指令。RISC-V由GCC和LLVM等编译器技术支持,可以处理其他指令。低功耗IOT应用程序可以通过在硬件中实现某些功能来受益于此方法。

RISC-V开始作为学术练习,但已经进入了商业空间的礼貌,如SiFive.SiFive的Freedom系列是真正的RISC-V核心实现。Freedom U500平台是一个RV64GC实现,而Freedom E500是一个RV32IMC/RV32EMC实现。该U500可通过台积电使用其28纳米技术。它支持缓存一致性的多核实现,支持高速外设,包括PCIe 3.0、USB3.0、千兆以太网和DDR3/4内存控制器。E500采用180纳米技术,支持片上闪存、OTP和SRAM。

那些不想深入定制芯片的人可以利用Microsemi的支持RISC-V的SmartFusion 2 fpga。Microsemi支持一系列RISC-V实现,最高可达128位RV128I。Microsemi的FPGA支持ARM的Cortex-M1,但如果要将设计从FPGA转移到定制的ASIC,则需要获得许可。RISC-V的情况就不同了。Microsemi包括一个完整的开发平台,包括其Libero FGPA IDE和基于eclipse的SoftConsole软件IDE。该系统包括图形配置工具。

RISC-V的简单性也可能在需要认证的安全和安全应用中有利。当然,ARM已经在它的一些平台上做到了这一点.

(顺便说一下,这篇文章的标题是改编自电影中的一句话短路.五号是机器人主角。)

此文件类型包括适用时的高分辨率图形和原理图。