你将学习:

- 如何实现一个倍频器。

- 如何在GreenPAK Designer软件中创建电路设计。

本文描述了如何实现一个频率乘法器使用GreenPAK可编程混合信号IC.该倍频器可用于各种应用,包括控制电路和通信设备。

术语和定义

- CD:计数器数据

- 问:计数器

- DCMP:数字比较器

- 有限状态机

看到表格下面为引脚配置。

完整的设计文件可在这个链接.本电路设计是在免费的gui基础上创建的GreenPAK设计软件,是Go配置软件集线器软件包的一部分。

设计概述

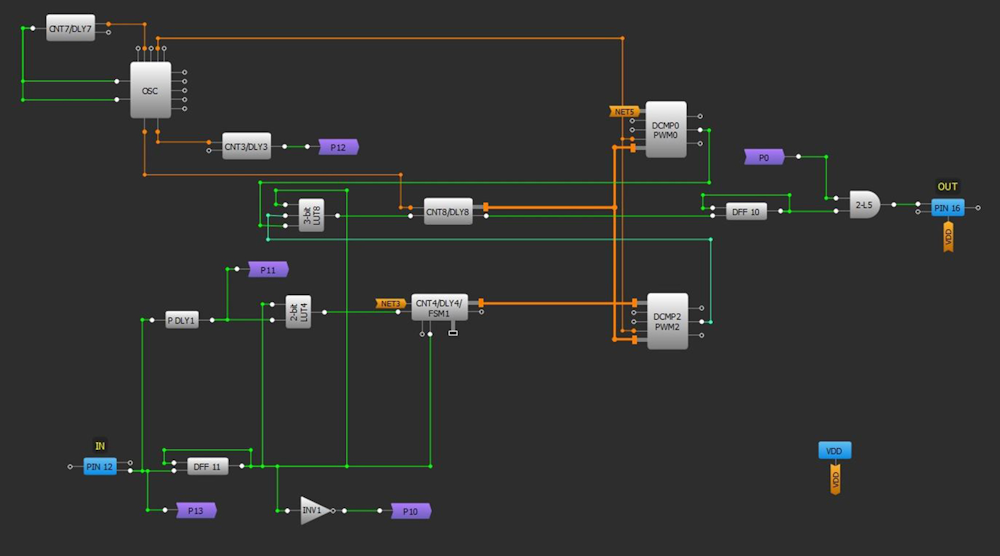

GreenPAK的整体设计见图1和2.

设计可分为以下几个部分:

- 倍频器

- 选择器

- 乘数的设置

- 国旗

- 出

倍频器

该设计包括FSM0/DCMP0和FSM1/ DCMP2两个倍频块,如图所示图3.

由FSM1/DCMP2组成的倍频块的工作原理如下:当选择器的信号为LOW时,FSM1计算IN频率;当选择器的信号为HIGH时,FSM1、CNT8和DCMP2产生OUT频率。

选择器

选择器选择这两个块中的哪一个计算输入频率,哪一个产生输出频率的乘积(图4).

乘数的设置

CNT3用于选择输入频率乘以的因数(图5).计数器数据由公式确定:

CD= 2 *N−1

其中CD为计数器数据,N为乘数。

CNT7用于确定输入频率。计数器周期大约为:

T≈1/(100∙F∙N)

其中T为计数器周期,F为近似输入频率,N为乘数。

国旗

对于给定的输入频率,电路多路复用范围在0.2x和5x之间。如果频率在这个范围之外,那么FLAG将是LOW(图6).

出

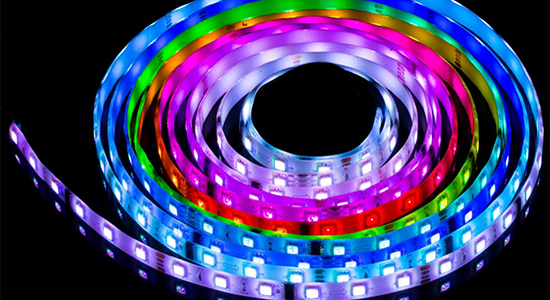

如果FLAG为HIGH, DFF10产生50%占空比的输出频率。如果FLAG为LOW,那么OUT将为LOW(图7).

例子

在一个例子中,考虑将~ 1khz的输入频率乘以15倍。计数器数据CNT3为:

CD = 2 * 15 - 1 = 29

CNT7的计数器周期应为:

T≈[1/(100∙1000 Hz∙15)]≈666 ns

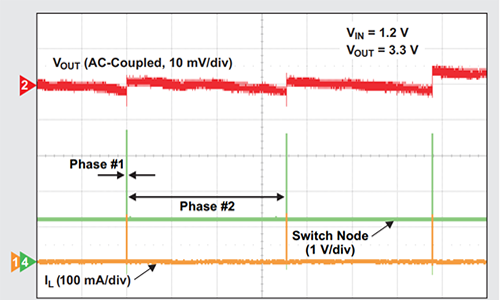

实验波形

图8通过12说明实验波形。

- 通道1(黄色/顶部线):PIN#12 (IN)

- 通道2(浅蓝色/第二线):PIN#4(旗帜)

- 通道3(洋红色/第三行):pin# 16 (OUT)

结论

本文演示了如何使用GreenPAK IC制作一个倍频器SLG46620芯片被使用,留下大量的块可用来构建其他电路。本设计的输入频率范围为电路所调试的典型频率(~ 1khz)的0.2 × 5倍。典型的输出频率不能超过135 kHz。

由于它的大小、可配置性和价格,GreenPAK提供了一种高效和低成本的方法来实现一个倍频器。